作者:电子创新网张国斌

Qorvo为地球提供连接、保护和动力,其产品遍布汽车、智能手机、可穿戴设备、医疗电子,甚至外太空。近日,在2025年Qorvo媒体日上,这家全球领先的射频与电源管理解决方案提供商全面展示了其在无线通信、物联网和数据中心等热点技术领域的最新进展,从Wi-Fi 8的射频挑战、UWB的多维扩展应用到集成化电源管理IC(PMIC)服务AI数据中心,Qorvo正通过系统级整合能力加速赋能智能终端与基础设施。

一、Wi-Fi 8时代:从高吞吐到“超高可靠性”的跃迁

随着Wi-Fi在家庭、企业、工业和交通等场景的全面普及,全球Wi-Fi设备累计出货已突破459亿台。Wi-Fi 7在2024年大规模商用后,市场正迅速向下一代标准Wi-Fi 8过渡。不同于此前聚焦传输速率和带宽,Wi-Fi 8将“超高可靠性”(Ultra High Reliability)作为核心价值,服务于工业物联网、远程医疗、AR/VR与AI实时应用等低延迟高稳定性场景。

Qorvo亚太区无线连接事业部高级行销经理Jeff Lin(林健富)在演讲中指出Wi-Fi 8(IEEE 802.11bn)不再盲目追求更高的吞吐率,而是引入更协调的网络管理机制(如多 AP协同、协调空间流复用、Target Wake Time可调度)以提供更低的延迟、更少的丢包率和更高的连接稳定性。

他还指出在Wi-Fi 6E和Wi-Fi 7已经使用的6GHz频段为在Wi-Fi 8时代将发挥更大的作用, 他表示6GHz频段的频谱资源丰富,能够容纳更多的信道,减少信道之间的重叠和干扰。同时,Wi-Fi 8通过分布式资源单元(dRU)技术,可以根据网络负载和用户需求灵活分配频谱资源,进一步提高频谱利用率。

此外,在6GHz频段,Wi-Fi 8的多AP协同(MAPC)能够更好地发挥作用。例如,通过协调空间重用(Co-SR)和协调波束成形(Co-BF)技术,多个接入点(AP)可以协同工作,优化功率输出和信号方向,减少干扰,提升网络吞吐量和可靠性。

他表示在办公室、商场、体育馆等高密度场景中,6GHz频段的高容量和低干扰特性能够有效缓解网络拥堵。Wi-Fi 8在6GHz频段支持多链路操作(MLO),允许设备同时连接到多个频段或多个AP。这不仅可以提高数据传输的可靠性,还能通过负载均衡优化网络性能。

他表示Qorvo作为Wi-Fi FEM(前端模块)与滤波器核心厂商,正围绕以下三方面发力:

1、非线性PA + DPD架构:通过引入数字预失真(DPD)补偿非线性放大器的输出,Qorvo大幅降低系统功耗,在Wi-Fi 7平台已取得出货量领先地位,他表示目前Qorvo与高通、博通等主控芯片厂商深度协同,让主流平台适配DPD算法,此外Qorvo提供全频段射频与滤波器组合方案,完整支持2.4GHz/5GHz/6GHz三频段,并兼容未来频谱动态调整,Qorvo的滤波器产品则覆盖Wi-Fi 6E/Wi-Fi 7/Wi-Fi 8,满足全球不同国家频谱合规要求。

2、Thermal Sensor + Power Level调节:他表示为了满足多用户场景下的动态功率分配需求,FEM需实现高、中、低功率多档输出,并融合温度传感补偿功能,提升频稳控制;

3、多协议共存优化:未来的家庭路由器将集成Matter、BLE、UWB等无线协议,Qorvo的滤波器和集成射频方案将成为避免干扰的关键。

他表示Wi-Fi 8预计将在2027年完成标准制定,2028年起大规模出货。Qorvo已率先启动与主芯片厂商的前期协作,推动iFEM(集成FEM+Filter)方案,构建其在下一代Wi-Fi市场的技术护城河。

二、UWB从“定位”走向“感知”:全栈式方案生态初成

目前,UWB(Ultra Wideband)作为高精度定位和安全通信的关键技术,正逐渐从工业资产追踪扩展至消费电子与智能出行。苹果、三星、Google等主流手机厂商已将UWB作为新一代标配通信模块;汽车行业通过CCC联盟推动UWB数字钥匙落地;CSA联盟的新标准Aliro也首次将UWB纳入智能门锁等场景。在此背景下,UWB市场正从“专业小众”走向“生态主流”。

Qorvo资深市场经理俞诗鲲在媒体日上表示,随着越来越多手机以及终端产品厂商支持UWB ,未来UWB有可能成为手机等设备的标配,另外,UWB已经不仅应用在高精度定位领域,更可能与蓝牙,NFC等融合,此外,通信技术的演进方向是“通信+感知”一体化,UWB本身就具备雷达感知能力,无需额外增加传感器,因此未来UWB的雷达感知应用在走热,如用在活体监测、生命体征检测、无感支付等新兴领域。

他表示Qorvo在构建“3+X”UWB技术框架,三就是:

高精定位:工业/医疗/物流资产追踪、无人车轨迹规划;

空间感知+安全认证:智能门锁、车载无钥匙进入、地铁门禁;

雷达微感:支持对呼吸/心跳/在座状态的非接触式检测;

X=雷达融合应用:车内留人、智慧家庭环境状态感知。

据他介绍,Qorvo在2025年3月推出了第三代首款全集成低功耗超宽带(UWB)片上系统QM35825,这款高性能、超低功耗SoC凭借基于雷达的传感技术实现精准定位追踪,适用于存在检测自动化、家用安全门禁、非接触式生命体征监测,以及个性化内容体验等场景。

“这里的全集成指它集成了 UWB收发器、MCU、前端放大器,支持双向测距(TWR)、TDOA、AoA等全定位协议,支持厘米级定位精度;发射功率达104dBm,并拥有片上人工智能(AI)及机器学习(ML)处理能力,显著提升测距精度与稳定性,适用于智能门锁、数字车钥匙、安防雷达、智慧医疗与家庭健康等。”他指出,“QM35825评估和开发套件将于6月起通过Qorvo全球分销商发售,套件包含完整的可配置软件包,以及示例应用和开发者工具。”。

此外,他表示在消费侧,随着头部手机品牌加速标配UWB,Tag配件、门锁、音箱将迅速形成使用闭环;在工业侧,Wi-Fi 7 AP集成UWB模块,天然完成UWB基站部署,为室内导航与资产管理提供基础网络。

目前,Qorvo通过芯片、模组、软件和天线定制服务构建“芯片厂商+生态服务商”的混合式增长路径,在工业、汽车、智能家居三大垂类构建差异化优势。

Matter:解锁智能家居“多协议”融合挑战的核心钥匙

随着智能家居市场的快速增长,不同厂商之间的设备互操作性成为了一个亟待解决的问题。为了使不同生态的智能家居产品可以做到互通互联,Matter协议应运而生,Matter 是由 Google、Apple、Amazon 等联合推动的新一代智能家居协议,它强调跨平台互通、安全性和简单性。据CSA联盟预测到 2027 年,将有 60 亿台智能设备具备 Matter 支持能力,智能家居协议将加速统一。

对于开发者而言,通过Matter协议,不仅可以简化开发过程 ,还能够促进技术的快速迭代 。在传统开发流程中,在不同生态系统的适配工作上需要耗费大量的时间和资源。而现在,开发者只需一次开发便能支持多种通讯协议,大大减少了重复劳动。

俞诗鲲表示尽管Matter协议能够允许不同的芯片或设备厂商在开源软件的基础上做自己的软件及应用,以确保每台设备接入后都能做到互联互通。但对于消费者而言,从传统的智能家居设备转移到支持Matter的设备的过程中,仍存在两个问题亟待解决。

向下兼容问题 :消费者本身已经拥有一些Zigbee智能家居设备,当购置新的支持Matter的智能家居设备后,会发现新的设备与之前的设备无法进行互联协作。

转发兼容问题 :当消费者购买了支持Matter的新设备后以及Matter的网关,尽管可以实现Matter不同设备之间的互通互联,但对于不支持Matter的设备,依然无法和这些设备之间实现互联。

俞诗鲲表示Qorvo推出的芯片多协议解决方案,特别是其专利的 ConcurrentConnect技术 ,能够在一颗芯片上集成Zigbee、Thread和蓝牙等多种通讯协议,显著降低了产品的设计难度和成本。

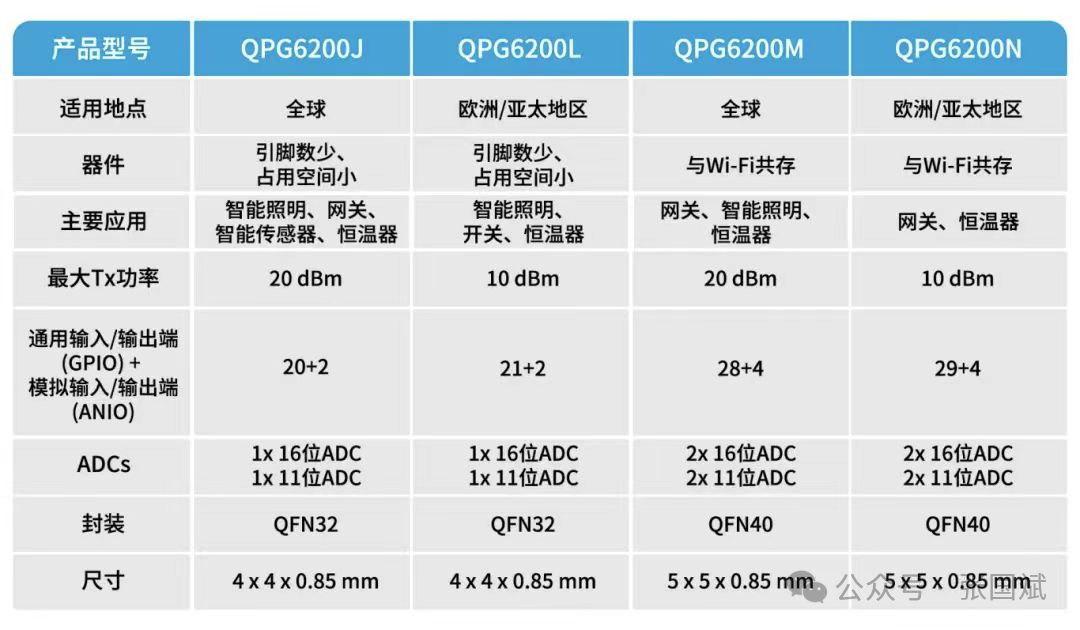

他以今年5月Qorvo全新推出的三款 Matter 系统级芯片(SoC)举例。这三款全新的 SoC 与此前发布的 QPG6200L SoC 同属 QPG6200 产品家族,QPG6200L 目前已与多家领先的智能家居 OEM 厂商合作量产,通过采用高能效架构和 ConcurrentConnect 技术,可真正实现 Matter over Thread、Zigbee 和低功耗蓝牙®的并发运行。紧凑型QFN40封装可提供高达20 dBm的发射输出功率,支持广泛的高性能智能家居应用。这一统一平台确保了全系列产品均具备高效可靠的多协议连接能力。

“QPG6200支持 BLE、Thread、Matter 三协议并发,兼容旧有 Zigbee/Thread 网络,具有独家“多连接(Concurrent Connect)”架构,具备 MAC 层独立信道管理能力,避免冲突与丢包。全面支持苹果、谷歌和三星三大生态,软硬件工具支持向后兼容架构。”他强调,“Qorvo 正在赋能‘即插即用’的 Matter 体验,让开发者聚焦产品创意,而非底层协议兼容挑战。”

三、助力AI数据中心:PLP集成式电源方案优化SSD设计

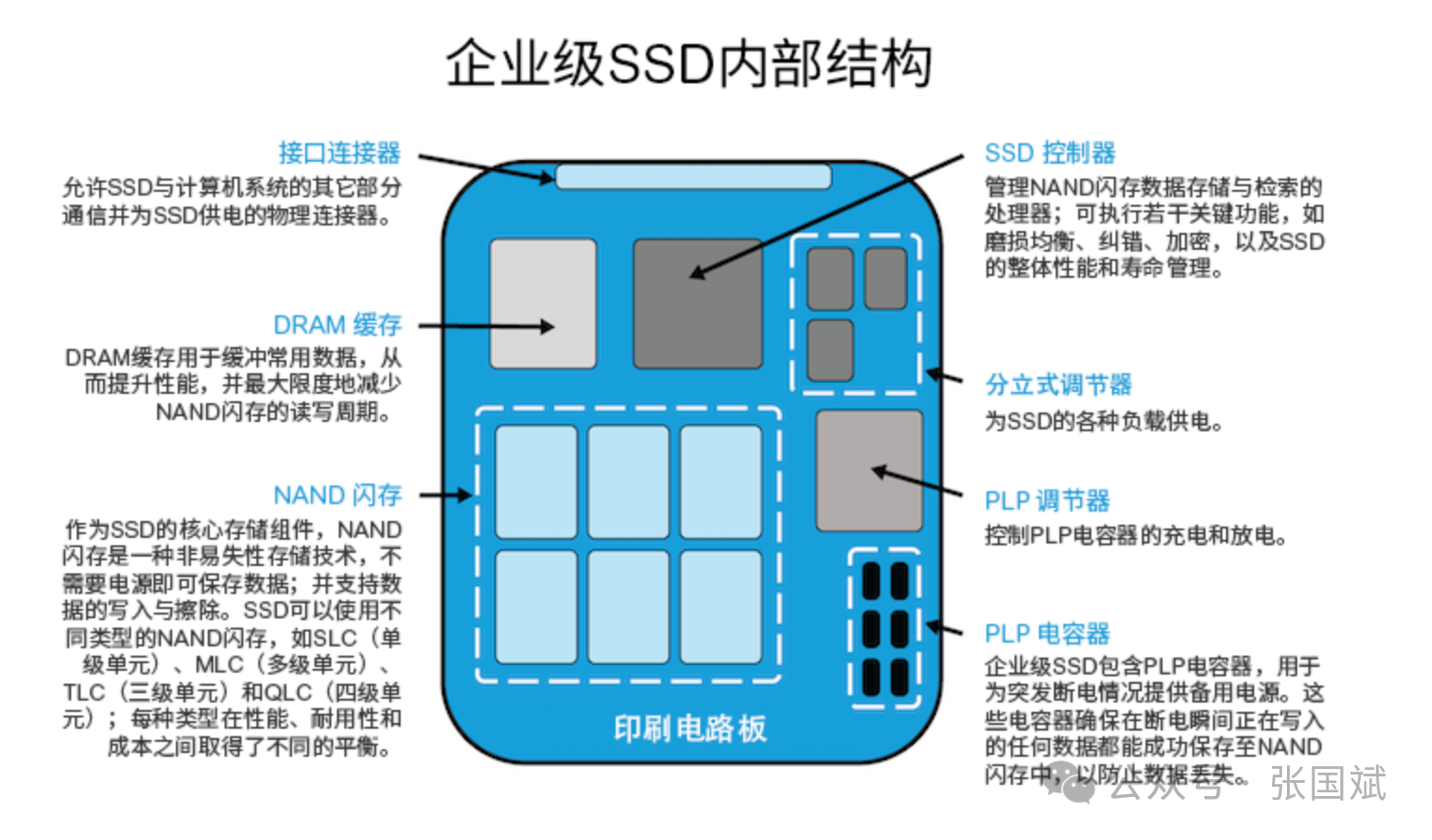

目前,在AI模型训练、云计算、边缘推理等应用爆发下,全球数据中心数量迅速增长。企业级SSD取代机械硬盘成为主流趋势,而高密度SSD必须解决功耗密度、热管理、掉电保护(PLP)等挑战。

根据 IDC 数据,2024~2028年企业级SSD出货量将以年复合18% 增长,数据中心用SSD 市场预计2026年达到580亿美元,以 ChatGPT、Sora、文生视频等 AI 工作负载为代表,每块服务器对高速 NVMe SSD 的需求已从单盘提升到4~8盘并行,这意味着,高密度SSD堆叠不仅带来存储挑战,更带来功耗管理挑战,传统线性稳压或片上LDO方案已难以满足性能与散热的双重需求。

Qorvo应用经理张俊岳在媒体日上指出,AI推动SSD架构进化:高IO性能要求SSD在断电时仍能保障数据完整;大型服务器群需更小更强大的电源管理IC;多颗芯片叠加使PMIC高度集成成为趋势。

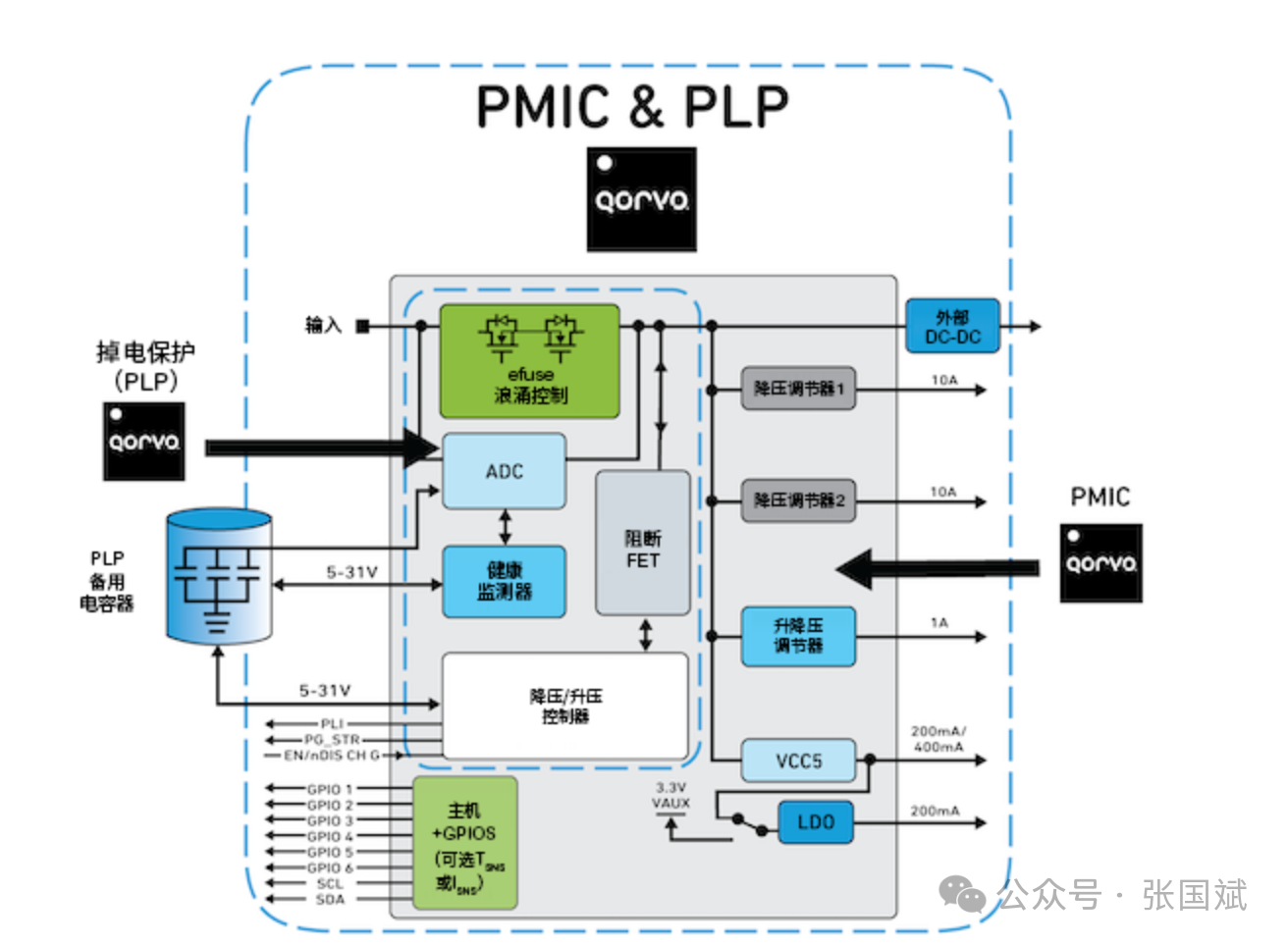

他指出Qorvo首先将电源断电保护(PLP)技术与PMIC集成,并通过集成eFuse、背靠背MOSFET、阻断MOSFET、储能电容管理和健康监测系统,为企业级存储设备提供了高可靠性的断电保护,确保了存储数据的完整性,目前Qorvo在这个领域处于全球领先地位。

他解释说SSD中的PLP在断电期间可提供足够的能量,将关键数据保存至NAND,PLP的主要任务是延长SSD的运行时间,以便安全地将数据从驱动器的临时存储移动到永久存储器,确保数据在系统重新通电后仍然存在且可访问。将SSD中的PLP和PMIC集成可以获得更多的存储容量。

“Qorvo 并非仅仅提供电源IC,而是将电源管理作为一种软硬件协同的系统能力:包括降压控制、掉电保护(Power Loss Protection)、热反馈调节、冗余容错等,通过将SSD电源管理纳入其连接系统的延伸,Qorvo 能在数据流的始发、传输、缓存、处理四个环节中实现端到端能效控制与系统协调。”他指出,“此外,Qorvo的PMIC已开始支持企业SSD主控SoC标准接口,加速SoC+PMIC+闪存三方生态集成。”

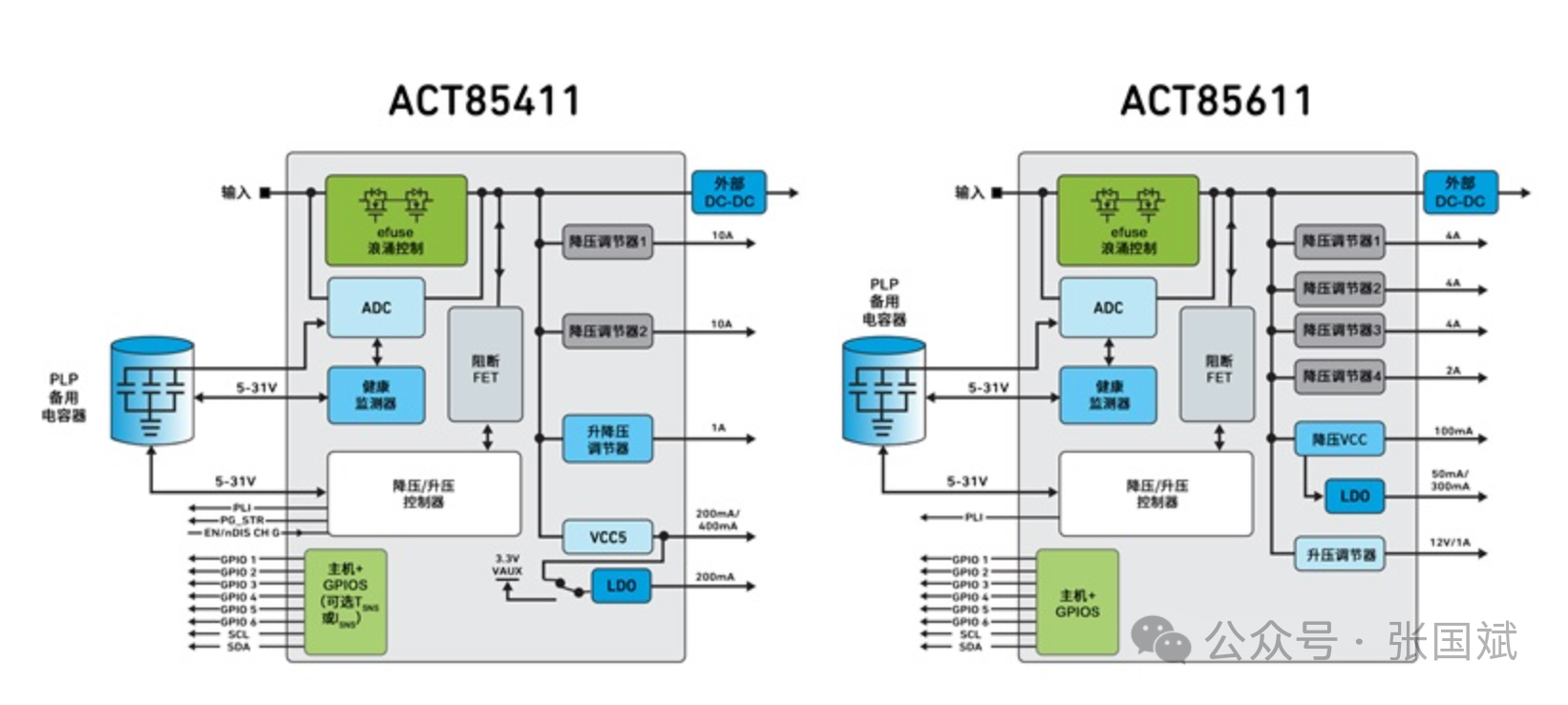

他举例说Qorvo的ACT85411/ACT85611两款芯片以SoC形态将多路DC/DC、eFuse、PLP控制与电容健康检测集成在单芯片中,他强调这样一颗芯片替代5颗分立电源器件,释放了存储面积,为NAND与DRAM让出空间;此外这样的方案内建电容健康监测与容量评估算法,实现动态容错强化了可靠性,另外,通过I2C接口快速修改输出电压与时序,适应不同盘型也实现了可编程化,这样的方案还可以降低系统BOM成本--通过高精度电容检测节省昂贵的高压电容使用量。

随着AI、物联网与智能生活场景的全面铺展,市场正从“单点突破”进入“系统协同”的新阶段。Qorvo以FEM+滤波器+模组+电源为核心,打造出“可规模部署+高性价比+生态友好”的全套连接与功率管理方案,以其强大的系统设计能力、产业链整合能力与射频/连接/电源三位一体布局,不断打破技术孤岛,形成面向下一代智能设备的坚实技术底座。从 Wi-Fi 8 的射频先锋、UWB 的多场景演进、Matter 的多协议融合到 SSD 的能效控制,Qorvo 正在为全球智能化发展提供强大底层支撑。

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利