Matt Sgriccia、Frank Sandoval和Ryan Persons

Heraeus Precious Metals North America Conshohohocken LLC

24 Union Hill Road

West Conshohohocken,PA 19428 USA

罗庆生,贺利氏电子,18015657860

摘要

40多年来,设计和制造传统混合电路的首选基板一直是氧化铝。它提供了正确电路操作所需的机械强度、电阻率和热性能。然而,在过去几年中,我们经历了混合技术向具有高度复杂、密集电路配置的电子设备的转变,这些电子设备比以前的设计产生更多的功率,从而产生更多的热量。这需要使用具有更高导热性的基板来正确管理传热和散热,以保持终端设备的最佳性能和功能。氮化铝显示的热性能为设计工程师提供了一种可靠的替代传统氧化铝的方法。

在创造新的令人兴奋的可能性的同时,氮化铝的使用也为厚膜供应商和电路制造商带来了一系列不同的挑战。由于热膨胀失配,以及在烧制过程中影响附着力的基板发生的化学变化,以前适用于氧化铝的厚膜浆料通常与氮化铝不相容。为了克服这一挑战以及高功率、高可靠性电路应用的性能要求,贺利氏开发了一种符合RoHS和REACH标准的新型厚膜浆料。此外,我们还开发了电阻浆料和兼容的玻璃釉。本文将讨论上述厚膜材料及其可靠性测试前后的关键性能。这包括导体的附着力、电阻值及其TCR。

关键词

附着力,氮化铝,可靠性,电阻,厚膜,TCR

一、导言

厚膜混合电路技术以一种基板和元器件集成形式出现了近60年【1】。与典型的覆铜线板相比,厚膜在更小的封装中提供了类似或优异的性能,具有更好的散热优势。传统上,用于印刷混合电路的基板是氧化铝。它成功地满足了大多数功能操作要求:体积电阻率、高温稳定性、低表面粗糙度、可接受的导热性,以及与用于制造导体、电阻器、电介质和玻璃釉的各种材料(玻璃、金属氧化物和贵金属)的兼容性。此外,它提供了一个宽的处理窗口,有助于最大限度地减少厚膜的性能变化。然而,市场已不断需求更高功率密度和更好热量的小型设备耗散以提高设备性能。为了有效地制作这些设备,热导率必须比氧化铝基板所能提供的还要高。为了满足这一要求,更具导热性的氮化铝基板得到使用。如表1【2】所示,根据制造商的不同,氮化铝的热导率可以比氧化铝高7.5到10倍,同时在相同的工艺窗口内仍保持类似的功能特性。

| 氧化铝 | 氮化铝 |

市场应用 | 混合电路/片式电阻 | 功率电子 |

优势 | 抗腐蚀性/低成本 | 高热导率 |

热膨胀系数(ppm/°C) | 6.0~7.0 | 4.0~5.0 |

热导率(W-m.k)@25°C | 20~30 | 150~230 |

弯曲强度(Mpa) | 400~500 | 450 |

断裂韧性(Mpa. m1/2) | 3 | 3 |

表1:氧化铝和氮化铝陶瓷基板的性能比较

出于上述原因,在电力电子和功率LED封装中,氮化铝似乎是比氧化铝更好的选择。然而,氮化铝还具有其他固有特性,这给厚膜供应商带来了挑战,尤其是在附着力方面。氮化铝的热膨胀系数比氧化铝低得多。厚膜电路常用的氧化铝为96%,其余主要为玻璃相,厚膜浆料中的玻璃和氧化铝96瓷中的玻璃相在烧结时形成键接,从而达到很好的附着力,但AlN表面却没有这些玻璃相,所以常规的用于氧化铝96瓷的浆料无法用于AlN上,且因为热膨胀不匹配可能导致零件烧制后弯曲和/或开裂。氮化铝在高于700°C的温度下也会氧化,通常用于氧化铝的许多玻璃会加速和增强氧化,产生游离氮,从而破坏薄膜,导致起泡,从而直接影响附着力以及导电性和电气性能。贺利氏通过开发一系列厚膜浆料产品允许在氮化铝上构建混合电路。我们将讨论各种多层混合电路,重点介绍几种导体(银、银钯、银铂、铜和金)以及两种电阻膏,玻璃釉。对于导体,我们将详细说明几个关键性能特性,如初始附着力和长期可靠性测试后的附着力,包括150°C老化附着力和85°C/85%RH(相对湿度)。将对金导体进行相同的测试;然而,附着力将基于金丝键合。对于电阻浆料,我们将在进行可靠性测试后测量电阻变化和TCR(电阻温度系数),无论是否使用上釉。

二、加工厚膜导体(银、银钯)

在2"x2"的Maruwa氮化铝(AlN-170)基板上印制了以下导体浆料:CL80-11157(Ag)、C2360(6:1 Ag/Pd)。在两个零件上进行了初始和重新燃烧的附着力试验。其余10个零件用于可靠性测试。其中5个用于150°C老化,5个用于85°C/85%RH试验。

对于银、银钯的导线通过线径为1.3 mil的280目/0.5 mil的乳胶膜不锈钢丝网,使用70硬度的刮板。印刷后,将零件流平10分钟并放置在150°C的箱式炉中10分钟,以确保浆料完全干燥。在烧结炉中停留10分钟的850°C峰值温度。

图1显示了每个导体的烧结微观结构的SEM图像。导体内的玻璃/金属氧化物在导体和基板之间的界面处形成了一层结晶,这会产生一种对粘合至关重要的机械粘合。CL80-11157(1a) 和 C2360(1b),结晶的的微观结构非常相似。这是因为导体具有类似的玻璃和金属氧化物化学性质。

图1:氮化铝厚膜导体的截面

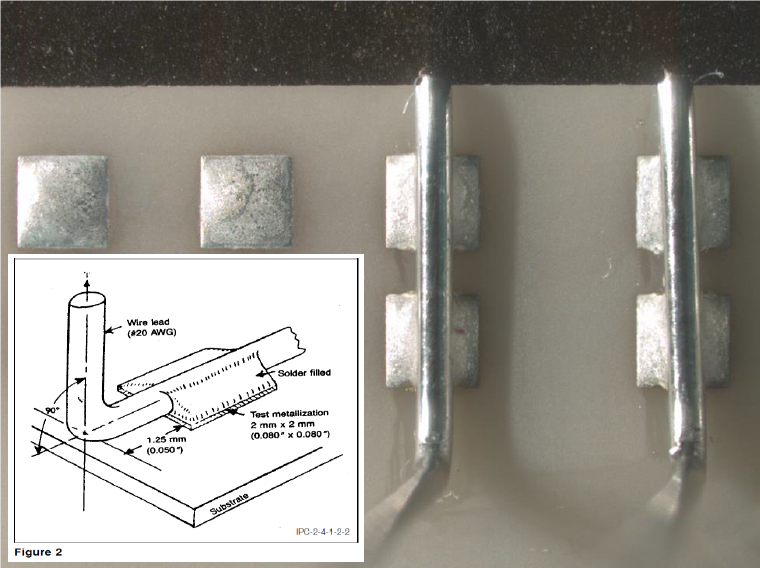

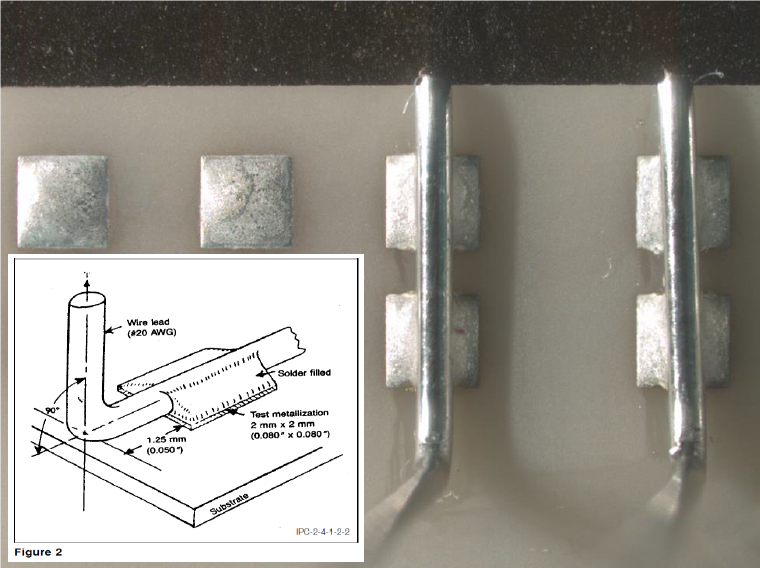

为了准备用于附着力测试的样品(图2),将锡铅丝焊接到每个已烧结的样品上的80 x 80 mil导体焊盘上。样品在250°C下浸入Alpha 615 RMA助焊剂并放入无铅SAC305(Sn96.5/Ag3.0/Cu-0.5)焊料中5秒钟。焊接后,引线弯曲成90度角。使用Zwick/Roell Z2.5剥离测试仪,移除电线并测量附着力。

图2:使用Alpha 615 RMA助焊剂在250°C下通过SAC305焊料对导体和导线连接至导体焊盘的可焊性测试

三、附着力性能评估

表2列出了各导体的特性。浆料的粘度和流变性适合丝网印刷应用。烧成膜厚度和电阻率测量基于之前概述的加工条件。

导体 | 粘度 (Pa.S, @Brookfield HBT, SC4-14, 10rpm, 25°C) | 固含量 (%) | 烧结膜厚 (μm) | 方阻 (mΩ/□) |

CL80-11157 (Ag) | 150~220 | 82~84 | 12~16 | <3@12μm |

C2360 (AgPd) | 150~220 | 82~84 | 13~17 | 15~20@15μm |

表2:导体浆料特性

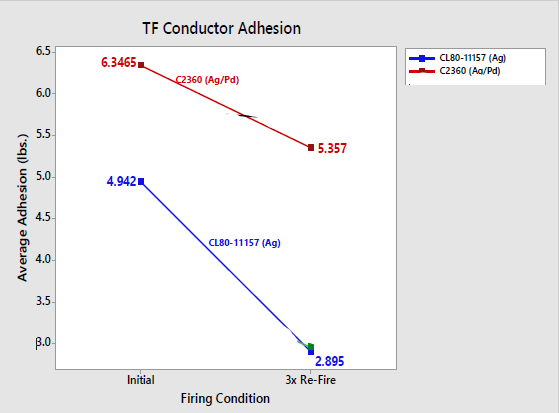

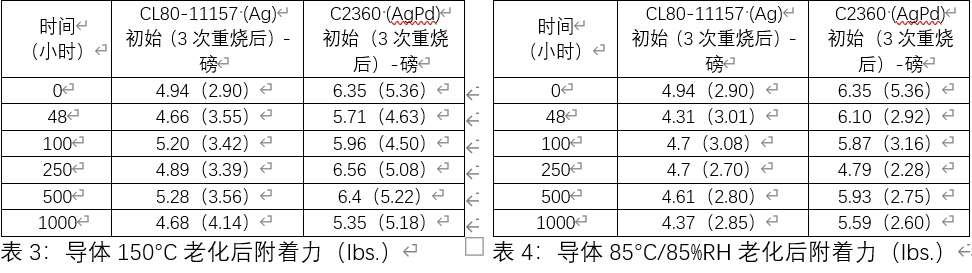

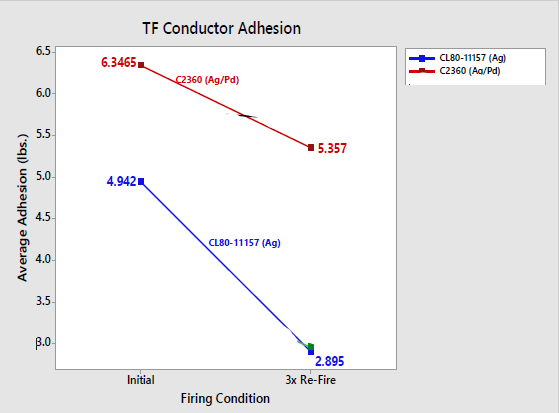

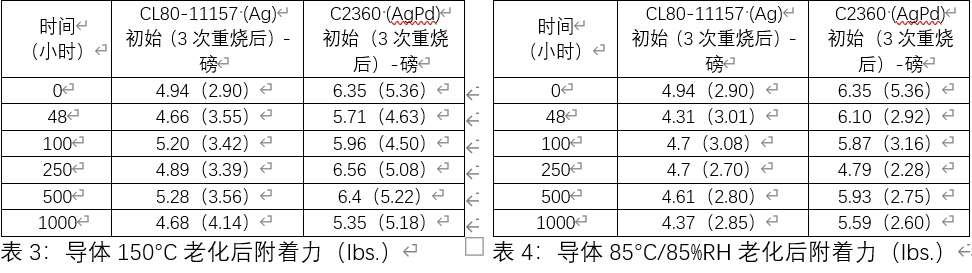

图3显示了初始和重复烧结的附着力结果。对于大多数应用,大于4.0磅的初始附着力值被认为是可以接受的。正如预期的那样,再次烧结后附着力降低。这可归因于多种因素:导体内玻璃成分的回流、玻璃/金属氧化物与金属颗粒反应方式的变化和/或与氮化铝基板氧化相关的化学反应。通常,再次烧结后,可以接受大于3.0磅的附着力。除CL80-11157(Ag)略低于外,C2360超过了3.0磅的附着力目标。表3和表4分别说明了150°C老化和85°C/85%相对湿度可靠性试验的结果。

图3:导体附着力(初始与3次重复烧结)

150°C老化结果(表3)表明CL80-11157(Ag)、C2360(Ag/Pd)导体的初始(1x烧结)附着力在1000小时后>4.0磅。老化后,CL80-11157(Ag)对于单次烧结的样品附着力几乎不变,但对于3次烧结的样品,附着力是增加的。

85°C/85%相对湿度研究的结果(表4)表明,所有导线的初始(1x燃烧)附着力均超过了4.0磅的目标值。再次,我们注意到多次烧结后的附着力在双85试验后有所降低。

四、金导体加工

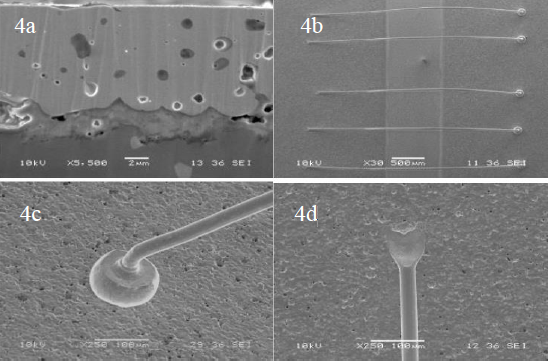

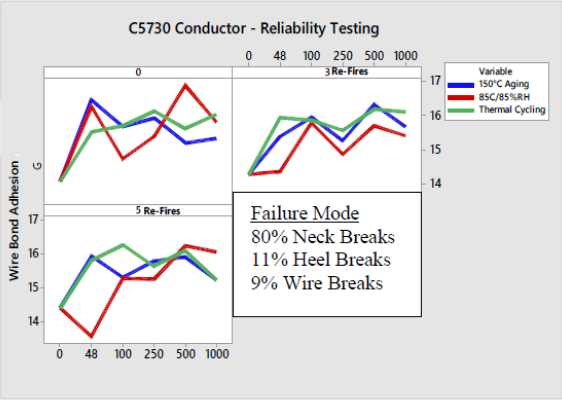

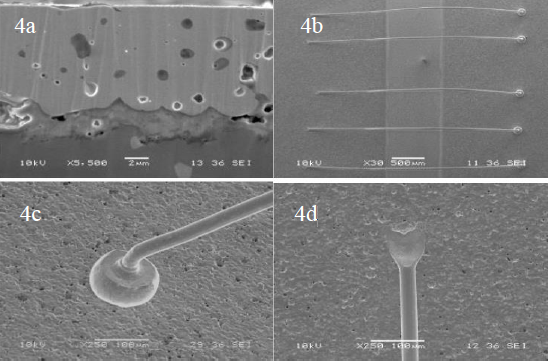

在2“x2”的Maruwa氮化铝(AlN-170)基板上印制一层C5730金导体。印刷、干燥和烧制试验条件与前面讨论的导体相同。烧成后,使用1.25密耳金丝,在2个样品(30次拉拔样品)上测量初次烧成、3次再烧成和5次再烧成的金导体附着力。图4显示了金的微观结构和引线键合。烧制导体的横截面用4a表示。与之前的导体(图1)的方式大致相同,在界面处形成了一层玻璃层,形成了一种机械结合,有助于提高附着力值。图4b显示了完整的导线键合,而4c和4d显示了4b中所示楔形键合和球形键合的高倍视图。粘结层干净,无开裂或分层迹象。在1x、3x、5x燃烧后,还对两个样品进行了附着力测试,以进行以下可靠性测试:在150°C和85°C下老化,在0、48、100、250、500和1000小时下进行85%相对湿度测试。

图4:C5730金导体在氮化铝上和金线键合的SEM照片。

金导体属性/性能评估

C5730金导体的粘度为280–380 Pa-s,使用Brookfield HBT粘度计在25°C温度下使用6R杯,SC4-14号轴,在10rpm下测量。在12μm的标准化厚度下,固体含量为84–87%,电阻率<5.5毫欧/平方。附着力结果见图5和图6。通常,金线粘结附着力>12克,界面断线是可取的。正如我们在图5中所看到的,初始和再烧结后的附着力没有统计差异。中值保持不变。

|

|

图5:初始和重新烧结后的1.25密耳金丝键合界面图 | 图6:可靠性测试后C5730初始和重复烧结导体上的金丝拉力结果 |

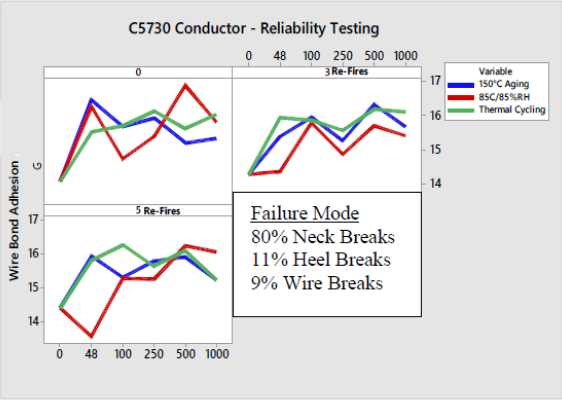

图6显示了150°C老化、85°C/85%RH和-55–150°C热循环可靠性研究产生的导线粘结附着力。结果表明,初始、3次再烧和5次再烧之间的附着力没有显著差异。此外,1000小时老化后、1000小时85°C/85%RH和1000次热循环后的值实际上大于初始附着力。数值范围为14-17克,远高于12克的目标值。

六、电阻器加工

最初为氧化铝开发的两种无铅电阻浆料与氮化铝具有良好的兼容性。R2211为10Ω/□电阻浆料,R2221为Ω/□电阻浆料。印刷、干燥和烧制条件与上述导体浆料相同。电阻器印刷在已有C2360(银/钯)导体的样品上。两个样品分别用于3次再烧和5次再烧试验。六个样品用于可靠性测试。两个样品用于150°C老化,两个样品用于85°C/85%RH,两个用于热循环(-55°C–150°C)测试。

还有六个样品印刷了玻璃釉浆料(IP9002)。IP9002通过200目筛网印刷,使用70硬度计刮板,钢丝直径为1.6密耳,乳胶厚度为0.5密耳。干燥后,在600°C下烧制,在峰值温度下停留5分钟。在这些样品上进行可靠性测试的方式与无釉的样品相同。在有釉和无釉的每个条件下,测量电阻变化以及+TCR和-TCR。

七、电阻器/印刷釉后特性和性能评估

表5列出了R2211和R2221电阻器的特性。

电阻 | 粘度 (Pa.S, @Anton Paar Rhysical Rheometer, CP25-10.100sec-1, 25°C) | 烘干膜厚 (μm) | 加玻璃釉的方阻变化 (mΩ/□) |

R2211 | 150~220 | 22~28 | 10±10% |

R2221 | 150~220 | 14~20 | 100±10% |

表5:电阻器印刷后情况

表6和表7列出了R2211和R2221电阻器在多次烧结后以及使用IP9002釉后的电阻变化。正如预期的那样,电阻随着多次烧结而降低。我们还观察到,在印刷有釉之后,电阻变化是可预测和可再现的。

电阻 | 重烧 | 电阻值 (Ω/□) | 变化率 (%) |

R2211 | 初始 | 11.04 | |

3次重烧 | 10.74 | -2.72 |

5次重烧 | 9.08 | -17.75 |

R2221 | 初始 | 99.29 | |

3次重烧 | 88.3 | -11.07 |

5次重烧 | 84.26 | -15.14 |

表6:电阻多次重烧变化

电阻 | 玻璃釉(IP9002) | 电阻值 (Ω/□) | 变化率 (%) |

R2211 | 无釉 | 10.64 | |

加釉后 | 11.09 | 4.23 |

R2221 | 无釉 | 101.25 | |

加釉后 | 102.81 | 1.54 |

表7:电阻有玻璃釉的变化

表8-10显示了在150°C老化、85°C/85%RH和-55°C–150°C热循环可靠性测试后,R2211和R2221与有IP9002釉的电阻变化。在150°C和85°C/85%RH下1000小时后,有釉的电阻变化小于5%,这在10%的典型行业标准范围内。同样,500次热循环后的变化在目标限值内。

时间 (小时) | R2211 无(有)玻璃釉 | R2221 无(有)玻璃釉 |

电阻值(Ω/□) | 变化率(%) | 电阻值(Ω/□) | 变化率(%) |

0 | 10.65(11.12) | | 100.56(101.96) | |

48 | 11.56(11.48) | 8.61(3.21) | 102.66(102.16) | 2.08(0.2) |

100 | 11.34(11.25) | 6.56(1.15) | 102.67(102.11) | 2.09(0.14) |

250 | 11.68(11.47) | 9.71(3.16) | 103.06(103.27) | 2.49(0.31) |

500 | 11.69(11.48) | 9.84(3.19) | 103.24(102.17) | 2.67(0.2) |

1000 | 11.56(11.35) | 8.60(2.10) | 103.44(102.08) | 2.86(0.12) |

表8:电阻变化(150°C老化)

时间 (小时) | R2211 无(有)玻璃釉 | R2221 无(有)玻璃釉 |

电阻值(Ω/□) | 变化率(%) | 电阻值(Ω/□) | 变化率(%) |

0 | 10.75(11.03) | | 105.69(103.29) | |

48 | 11.29(11.30) | 5.04(2.41) | 105.48(103.66) | -0.19(0.35) |

100 | 11.35(11.34) | 5.64(2.82) | 105.98(103.88) | 0.28(0.57) |

250 | 11.45(11.44) | 6.51(3.72) | 105.80(103.99) | 0.11(0.68) |

500 | 11.56(11.46) | 7.57(3.87) | 105.56(104.19) | 0.83(0.86) |

1000 | 11.62(11.53) | 8.18(4.47) | 107.03(104.46) | 1.27(1.13) |

表9:电阻变化(85°C/85%相对湿度)

时间 (小时) | R2211 无(有)玻璃釉 | R2221 无(有)玻璃釉 |

电阻值(Ω/□) | 变化率(%) | 电阻值(Ω/□) | 变化率(%) |

0 | 10.64(11.12) | | 105.69(103.29) | |

48 | 11.57(11.54) | 8.73(3.81) | 105.48(103.66) | -0.19(0.35) |

100 | 11.51(11.48) | 8.15(3.30) | 105.98(103.88) | 0.28(0.57) |

250 | 11.44(11.48) | 7.52(3.30) | 105.80(103.99) | 0.11(0.68) |

500 | 11.91(11.68) | 11.90(5.09) | 105.56(104.19) | 0.83(0.86) |

表10:电阻变化(TC:-55°C–150°C)

表11-12显示了150°C老化和85°C/85%RH(有或没有IP9002釉)后的TCR值。热TCR测量在125°C下进行,冷TCR测量在-55°C下进行。在老化研究中,当用玻璃釉时,两个电阻器的热TCR和冷TCR变化很小。而在85°C/85%RH研究中,有釉层时TCR的变化很大(表12)。

时间 (小时) | R2211 无(有)玻璃釉 | R2221 无(有)玻璃釉 |

HTCR (ppm/°C) | CTCR (ppm/°C) | HTCR (ppm/°C) | CTCR (ppm/°C) |

0 | 30.27(55.79) | -75.49(-28.14) | -40.19(-46.32) | -117.81(-121.94) |

48 | -1.26(33.36) | -62.45(-55.94) | -41.48(-49.15) | -129.91(-121.28) |

100 | 52.97(89.26) | -79.62(-59.31) | -27.73(-45.03) | -156.60(-118.29) |

250 | 21.93(32.46) | -86.05(-67.72) | -42.90(-51.17) | -119.22(-124.39) |

500 | 26.06(33.79) | -85.22(-63.98) | -51.92(-53.75) | -124.48(-126.02) |

1000 | 18.14(27.97) | -93.06(-71.54) | -48.86(-54.64) | -122.82(-126.28) |

表11:热态和冷态TCR(150°C老化)

时间 (小时) | R2211 无(有)玻璃釉 | R2221 无(有)玻璃釉 |

HTCR (ppm/°C) | CTCR (ppm/°C) | HTCR (ppm/°C) | CTCR (ppm/°C) |

0 | 26.37(55.71) | -85.59(-29.71) | -41.51(-43.46) | -124.78(-116.75) |

100 | 38.10(58.17) | -184.02(-59.55) | -48.67(-42.34) | -152.43(-116.95) |

250 | 42.68(59.65) | -170.40(-50.78) | -32.23(-43.83) | -147.49(-116.05) |

500 | 24.73(50.91) | -166.88(-51.87) | -54.23(-44.33) | -144.50(-115.81) |

1000 | 10.19(46.29) | -154.42(-76.71) | -59.53(-44.13) | -143.53(-117.66) |

表12:热态和冷态TCR(85°C/85%相对湿度)

八、结论

贺利氏已开发出用于氮化铝基板的符合RoHS和REACH兼容的无铅厚膜浆料,这包括银、银/钯和金导体,以及两个具有兼容玻璃釉的电阻浆料。所提供的数据清楚地表明,这些产品的性能特征与为氧化铝基板设计的传统厚膜浆料相似。对于大多数导体,可靠性测试前后测得的附着力值满足标准工业厚膜要求。与导体非常相似,10欧姆和100欧姆电阻器可产生良好的性能结果。这包括可重复生产的稳定阻值、优异的再烧性以及在进行可靠性测试后(无论是否有玻璃釉)可预测的TCR值。

目前贺利氏开发的用于AlN基板的材料如下表所列:

| 产品名称 | 型号 | 注明 |

1 | 金铂钯导体 | C6029A | 可锡焊,可键合 |

2 | 钯银导体 | C2330 | Ag:Pd=3:1 |

3 | 钯银导体 | C2360 | Ag:Pd=6:1 |

4 | 银导体 | CL80-11157 | 可电镀 |

5 | 金导体 | C5730 | 可键合 |

6 | 介质 | IP9241 | 850度烧结 |

7 | 电阻 | R2200系列 | 无铅 |

8 | 玻璃釉 | IP9002 | 500~600度烧结 |

所以该系列产品为需要使用氮化铝改善散热的应用提供了理想的解决方案。这解决了工业对高密度汽车混合动力车、加热器总成和LED照明的需求及更多功率电子产品的应用。

参考文献

【1】 R.G.Loasby和P.J.Holmes“厚膜技术的发展(书体,书名和编辑)Keith Pitt”,《厚膜技术手册》第二版。Keith Pitt Ed. Electrochemical Publications Limited,2005年,第1章,第23页。

【2】马鲁瓦-http://www.maruwa-g.com/e/products/ceramic/ceramic-substrate-3.html