作者:Imagination Technologies

8月21-23日,2024年RISC-V中国峰会在杭州黄龙饭店举行。作为已推出多款Imagination Catapult系列RISC-V CPU半导体知识产权(IP)的提供商,以及全球领先的GPU和AI加速器IP厂商,Imagination Technologies积极参与了此项中国大陆规格最高、规模和影响力最大的专业会议之一,并在大会现场展示了其RISC-V CPU+GPU集成优化平台。Imagination专家就如何利用系统性创新加速RISC-V CPU的采用和普及、借助GPU在智能化时代加速RISC-V CPU的落地和产业化、以及在汽车应用中发挥RISC-V架构的优势等话题,以及公司的展示与演讲反映了RISC-V的多个发展趋势而得到与会专业人士广泛关注。

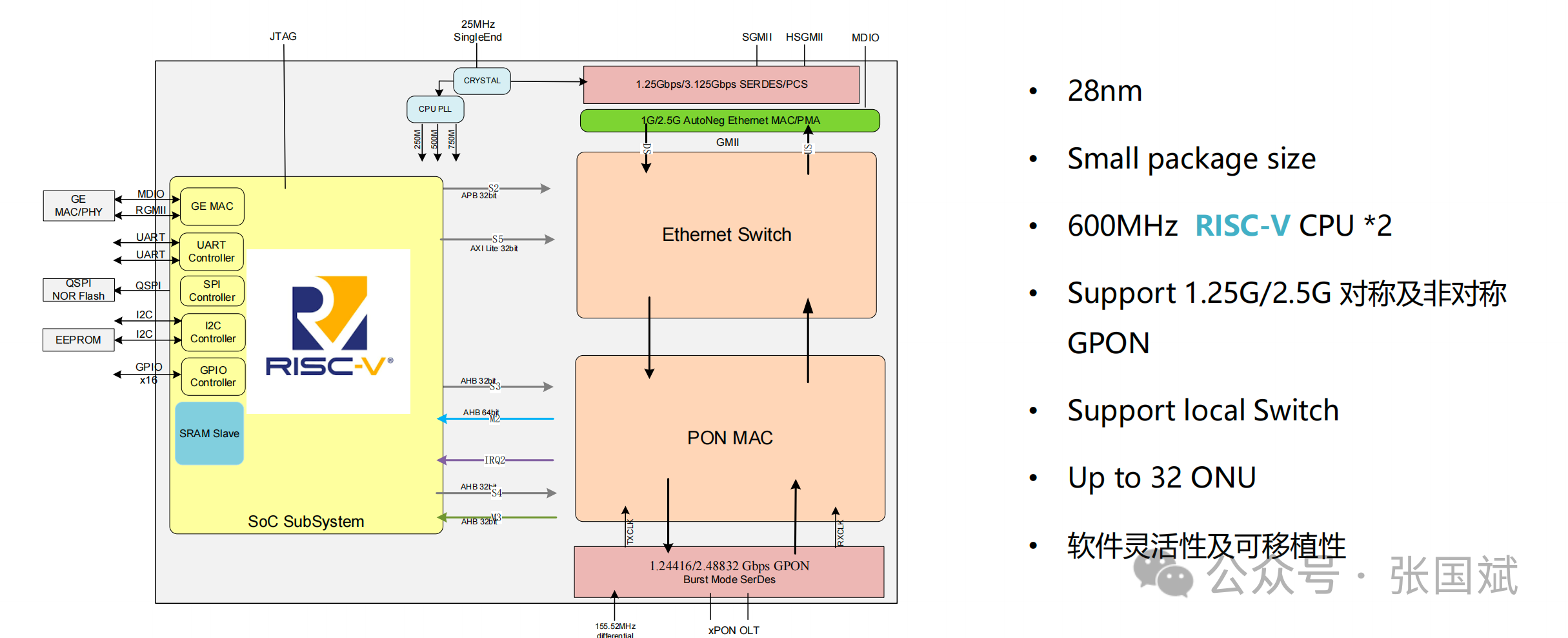

Imagination在CPU领域早已布局并积极拥抱和推动RISC-V,公司是RISC-V国际基金会的早期会员和开发工具等相关工作组领导成员,以及“RISC-V软件生态促进组织(RISE)”的创始成员,长期致力于RISC-V相关标准的制定和技术的开发,承担RISC-V基金会开发工具工作组的组织协同工作,为RISC-V的技术发展和生态繁荣做出贡献。公司也积极推动RISC-V产品的开发和应用,在2022年6月推出Catapult系列CPU中首款32位高实时性嵌入式RISC-V CPU RTXM-2200,并于近期推出了64位高性能密度应用处理器APXM-6400。

作为本届峰会黄金赞助商,Imagination积极参与了主会议、技术研讨会、展览展示和同期活动,带来了最新的 GPU、CPU、AI 等技术演示,以及三场主题演讲和专题演讲活动,全面展示了RISC-V技术和生态的发展趋势。

基于高性能RISC-V的集成优化平台大放异彩

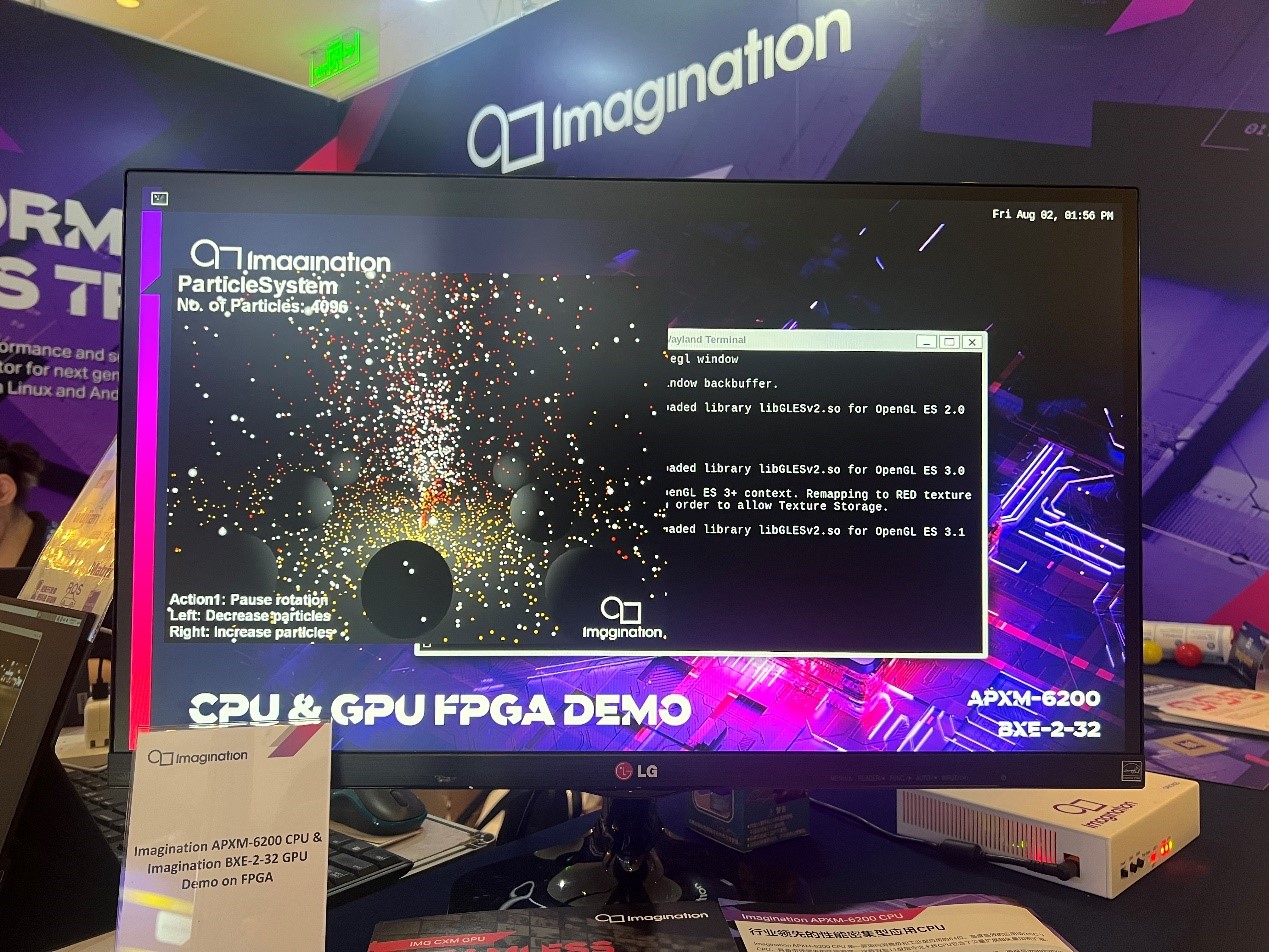

在峰会现场,Imagination展出了采用其最新发布的APXM-6200 CPU与其BXE-2-32 GPU核集成设计打造的CPU+GPU完整解决方案。作为RISC-V处理器性能向上的代表,Imagination APXM-6200 CPU是一款64位按序RISC-V应用处理器,带有双发射11级指令流水线,可为消费和工业应用工作负载提供同类产品中最佳的性能密度。与一些业界熟悉的应用处理器IP相比,APXM-6200大幅缩小了片芯占用面积,同时性能密度高出这些产品数倍到十倍。

作为一款依靠高性能和低平台迁移难度来获得用户信任的RISC-V应用处理器,APXM-6200可以根据客户的性能需求选择单核、双核和四核配置,并通过每核功率控制实现最高系统效率和缓存连贯性。该处理器在保持高性能、高灵活性的同时,还支持RISC-V矢量扩展并具有专门针对AI加速器的快速数据耦合,这使芯片设计工程师能够更轻松实现RISC-V+AI加速器,如与Imagination的全系列GPU IP实现高效和高安全性集成,从而在提升系统性能的同时还省去了大量的开发和验证工作量。

在其题为《推动RISC-V普及,Imagination推出革命性CPU和GPU集成解决方案》的演讲中,Imagination计算部门副总裁Shreyas Derashri表示:物联网和消费性产品领域一个非常明显的趋势是嵌入式计算正在催生集成化程度越来越高的优化计算平台,基于RISC-V的CPU通过预先集成的方式与GPU和AI/NPU等加速计算单元形成了功率效率、总线利用率和存储带宽利用率都更高的新型优化计算平台。

这种系统化的设计和生态化的合作,也成为了RISC-V开放指令集架构的一个新优势,从而推动了高性能的RISC-V CPU去适应和满足许多新的应用场景,为RISC-V的下一步发展创造了新的机会。同时,由于今天的智能化应用中需要处理的大量信息是图像和语音,因此GPU作为智能化计算加速器的用武之地越来越多,超过40%的半导体应用场景需要使用GPU来进行处理,这在安卓等应用市场上已经非常明显,因此RISC-V+GPU集成化计算平台的重要性不言而喻。

更高性能的应用带来繁荣的新生态

在前三届RISC-V中国峰会上,多数RISC-V厂商的展示和介绍都以突出的领域应用性能指标来替代其他架构的32位MCU产品和嵌入式方案,或者以定制化的模式来吸引用户的关注和采用。然而本届峰会的热点是,诸如Imagination等多家领先的厂商带来了高性能技术和产品,全面反映了RISC-V技术和产品正在多个方向上实现性能向上突破,同时加上RISC-V架构的开放性和安全性,正在吸引越来越多的在其他架构上已经验证过的硬件、软件栈、框架和应用开发合作伙伴,成为服务器和边缘智能等新应用的架构选择。

Imagination产品市场总监郑魁在主题为《Imagination GPU赋能RISC-V产业化落地和生态创新》发言中提到:随着诸如Imagination APXM-6200 CPU这样的64位高性能RISC-V应用处理器不断面市,加上行业中不断涌现的各种通用和开源智能计算框架和工具,为RISC-V + GPU + AI集成化智能处理平台提供了巨大的推动力。Imagination作为同时提供RISC-V CPU、多样化的GPU和AI加速器产品供应商,我们预判边缘智能应用将加速走进市场。

Imagination在本届峰会上的APXM-6200 CPU + Imagination B系列GPU现场演示吸引了众多行业人士驻足了解详情,虽然该演示只是一个运行在FPGA上的演示板,但是对于许多中国芯片设计公司,以及他们下游能够快速整合各种AI框架和开发工具的系统厂商而言,这意味着他们可以以非常快的速度针对不同的应用场景,开发出目前市场上十分火爆的嵌入式/边缘智能和推理计算盒子,从而以高性价比和能效来满足嵌入式和边缘智能需求。

全面周详的产品设计推动实际应用

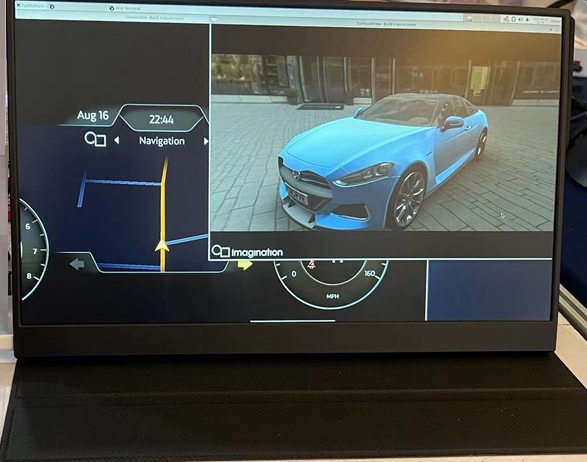

作为RISC-V生态最重要的GPU合作伙伴,Imagination在本次峰会上展示了360度环视以及汽车电子仪表盘演示。智驾芯片供应商可以利用这种同时满足ISO26262功能安全(FuSa)要求的RISC-V和GPU IP组合,针对传统的域控制机制或者新兴的区域控制模式快速开发高性能、高确定性和芯片面积更加优化的智驾芯片,并借助Imagination长期以来在汽车行业得到广泛应用和充分验证的Hyperlane技术去实现硬件虚拟化,全面满足汽车应用对高性能、高可靠性和高安全性的综合需求。

在本届峰会上,Imagination CPU产品管理部门总监Matthew Bubis发表了题为《RISC-V架构用于高完整性、功能丰富的汽车应用》的专题演讲,他表示:汽车市场对所有半导体厂商都充满了吸引力,但是在这个市场中的关键因素是质量(Quality)、可靠性(Reliability)、安全性(Safety)和可实现性(Availability)等“汽车产品四性”;同时因为新车型开发速度越来越快,因此为领域特定应用开发专用芯片或者IP并不是一种合理、高效和有效的方法,这个市场需要的是同时兼顾汽车产品四性的可扩展架构。

RISC-V架构为汽车芯片设计师和工程师带来了更大的自由度和应用发挥空间,因而它比其他的ISA更适合用在汽车电子系统中,特别是在汽车软件和工作负载异常复杂的今天,包括但不限于人机界面(HMI)、驾驶辅助和自动驾驶(ADAS/Autonomy)以及全面的人工智能/机器学习(AI/ML)。为此,Imagination选择推出了“RISC-V CPU + PowerVR GPU”的汽车IP平台,它可以最高效地支持图形处理、各种计算、硬件虚拟化和智能化等现代汽车功能。

这种组合并不是Imagination汽车IP平台的全部,更为重要的是其可以同时确保性能和汽车产品四性的IP开发流程,通过引入诸如基础危害分析 (PHA) 和故障模式及影响分析 (FMEA)等多项创新,该公司的系统级开发流程通过了最为严格的ASIL-D认证,因此其B系列和D系列PowerVR GPU也顺利地通过了严格的ASIL-B认证。当然,Imagination的RISC-V系列CPU也采用了同样的开发流程,可以确保其能够满足严格的汽车产品四性。

同时,Imagination在预先集成RISC-V CPU和GPU的时候,还进行了进一步的创新,实现了高安全性和可靠性的耦合以及更好的PPA性能,使下游的芯片设计厂商和最终的tier-1和车厂都能得到关键组件和系统层面都具有功能安全性(FuSa)的解决方案。正是通过这样全面周详的IP开发流程、高性能密度等功能性、以及从组件到系统层面的安全性和可靠性设计,确保了RISC-V处理器在汽车市场的应用。

本届RISC-V中国峰会已经落幕,但是Imagination等公司在峰会上通过推出高性能的RISC-V CPU IP、通过提供RISC-V CPU + GPU/加速器等解决方案、以及可以确保RISC-V CPU的可靠性和安全性系统方法,彰显出RISC-V在已经取得初步成功的32位MCU、嵌入式处理器和SoC之外,在更多的高价值市场上充满了机会。