双脉冲测试是表征功率半导体器件动态特性的重要手段,适用于各类功率器件,包括MOSFET、IGBT、Diode、SiC MOSFET、GaN HEMTs。同时,这项测试发生在器件研发、器件生产、系统应用等各个环节,测试结果有力地保证了器件的特性和质量、功率变换器的指标和安全,可以说是伴随了功率器件生命的关键时刻。

随着先进功率器件的问世以及功率变换器设计愈发精细,器件研发工程师和电源工程师都越来越关注双脉冲测试。

工欲善其事,必先利其器,拥有一套双脉冲测试平台是获得正确评估结果的第一步。本文将破解双脉冲平台搭建的难题,快来看看吧。

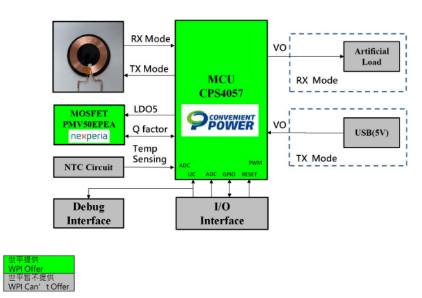

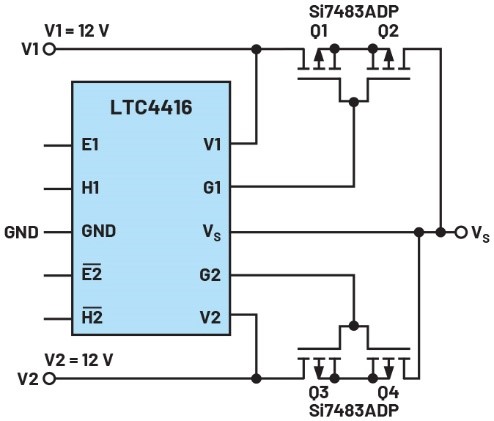

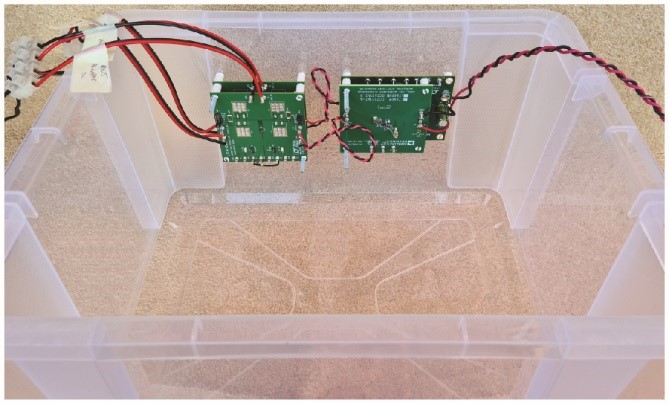

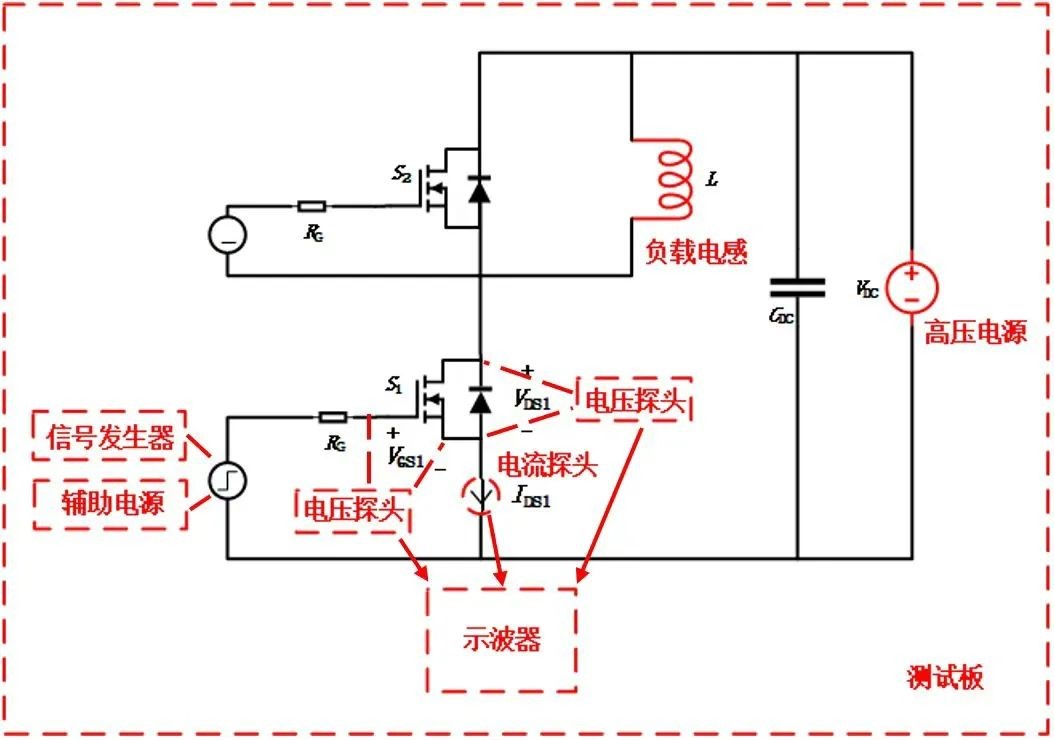

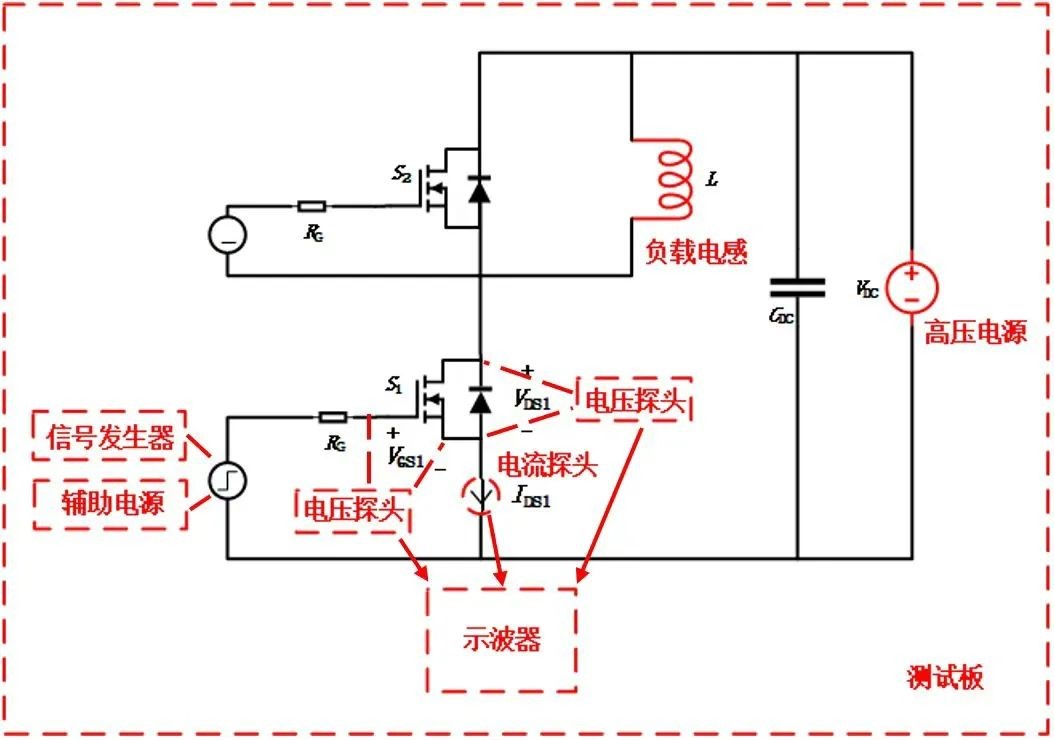

下图是双脉冲测试平台架构,并不复杂,主要包括:测试板、高压电源、辅助电源、信号发生器、负载电感、示波器、电压探头、电流探头。

测试板

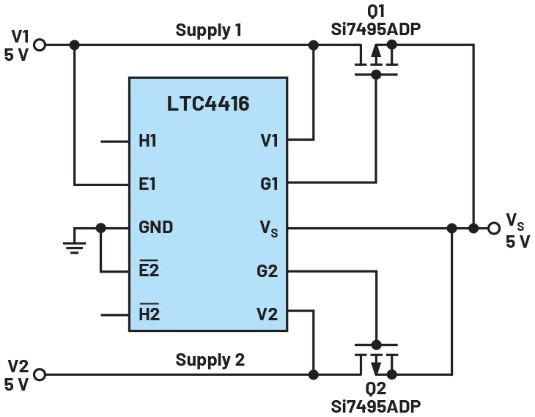

测试板是完成双脉冲测试的核心,一般为半桥电路,有时也会采用根据实际系统应用的拓扑。其上主要部件包括母线电容、驱动电路,母线电容为测试过程提供稳定的母线电压和所需的电流,驱动电路控制器件完成开关动作实现双脉冲过程。

测试板的优劣直接影响到评估结果的正确性。测试板需要首先需要确保在测量无误的情况下不出现异常波形,比如电压尖峰超过器件耐压值、无法解释的震荡、桥臂短路等,否侧这样的测试结果是没有价值的。对于服务于系统应用器件选型的测试需求,测试板可以直接选用变换器实际的电路板,这样的测试结果可以直接用于电路设计。随着器件的开关速度越来越快,对测试板的性能也提出了更高的要求,如回路电感、驱动电路等,对此大家可以参考我们之前的文章“双脉冲测试板盘点——SiC MOSFET 测试必备”。

Infineon公司推出了1200V CoolSiCTM MOSFET评估平台、含主电路+驱动的分立器件评估板、含主电路+驱动的模块评估板、模块驱动板,共4类评估板。

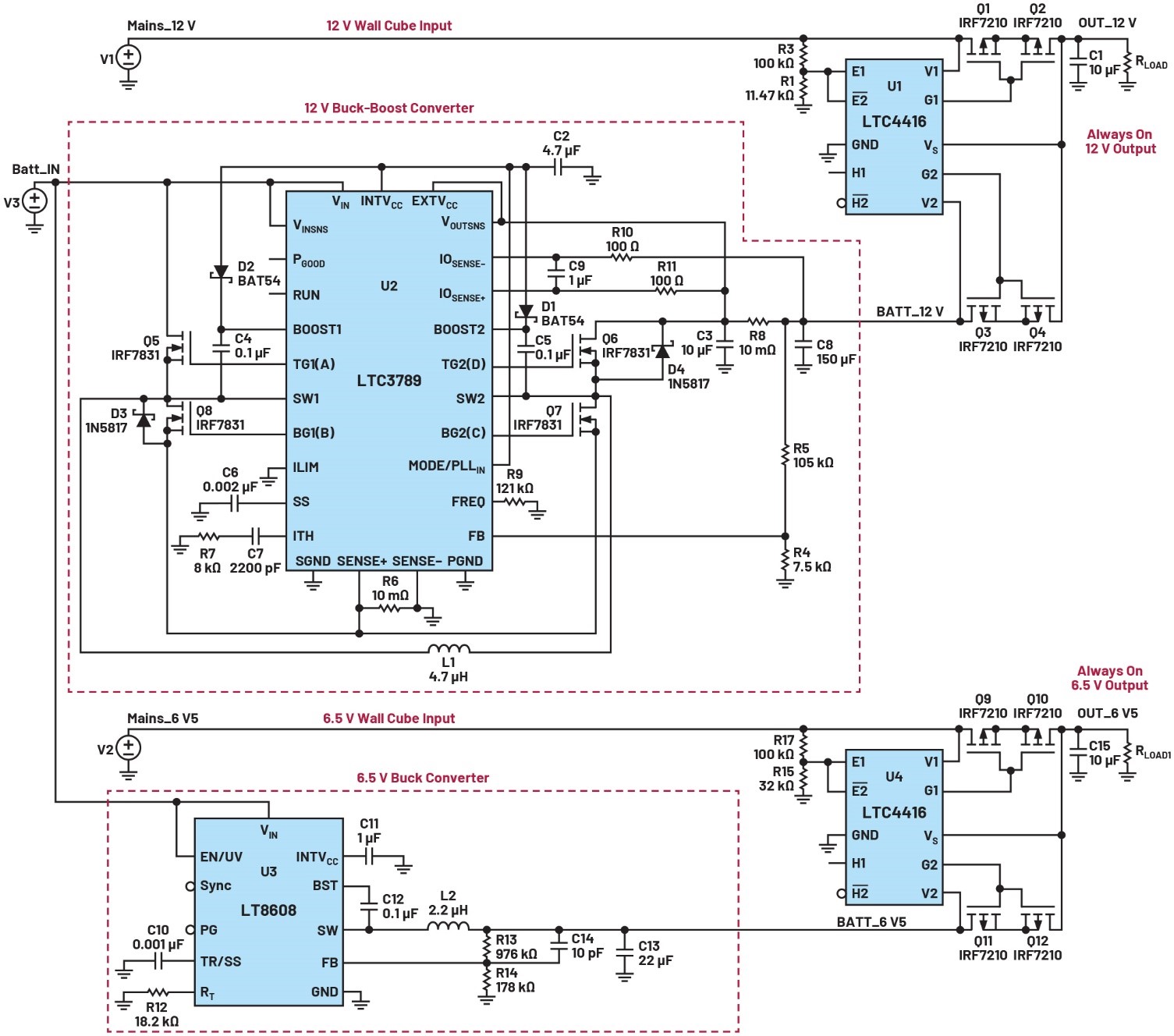

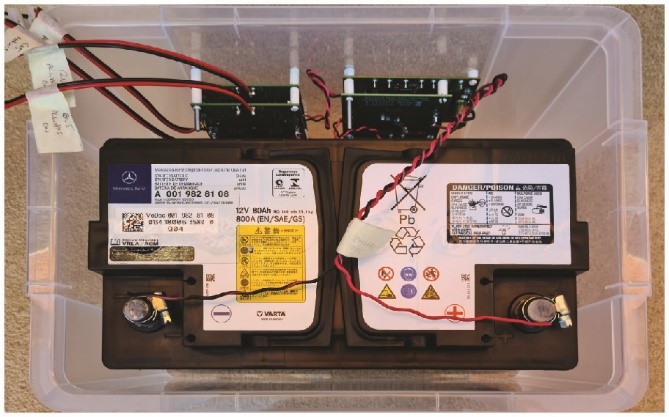

高压电源

高压电源在测试开始之前为测试板上的母线电容充电,起到设定测试电压的作用。母线电容容值一般较大,从几十uF到几mF不等,这就要求高压电源对容性负载的稳压能力要强。双脉冲测试中,测试电压一般不超过器件的耐压值,故可以根据被测器件的电压等级来确定高压电源的电压输出能力。同时,同一双脉冲测试平台往往会用于测试不同电压等级的器件,这就要求高压电源的输出电压精度需要满足测试要求。

此外,在双脉冲测试中,测试电流是由被充满电的母线电容提供的,高压电源在测试过程中并不提供能量。故高压电源可以选择功率较小的型号,一方面可以节约成本,一方面可以降低噪声。

高压电源可以选择泰克吉时利的2260B-800-2直流电源。

辅助电源

辅助电源的作用是为测试板上的驱动电路供电,所需电压一般在20V以内,所需功率一般在20W以内。同时,对于上下管都是开关管的测试板,可以选择双通道输出的辅助电源为上下管的驱动电压分别供电;对于三电平电路的双脉冲测试,可以选择三通道输出的辅助电源为每个器件的驱动电压分别供电。这样的好处是可以提高测试电路的可靠性,不会因为某一驱动电路故障而影响其他驱动电路。

辅助电源可以选择泰克吉时利的 2220 / 2230 / 2231系列直流电源。

信号发生器

信号发生器的功能是向测试板上的驱动电路发出双脉冲信号,完成双脉冲测试。由于测试所需的双脉冲信号频率不高,且其上升下降速度对测试的影响很小,故选择各厂商能提供的最基础的型号发生器即可。

不过需要注意的是,对双脉冲测试平台进行改造后还可以进行多脉冲测试、短路测试、雪崩测试、电源开环测试,此时往往所需的控制信号就不止一路了。所以在搭建双脉冲测试平台时可以选择双通道输出的信号发生器,以提高灵活度。

同时,在进行双脉冲测试时,需要不断根据测试条件调整双脉冲信号的脉宽和间隔,老式的信号发生器需要手动输入编辑波形或上位机编程来实现,十分不方便。针对这个问题,可以选择泰克科技的AFG31021(单通道)或AFG31022(双通道)信号发生器,其上搭载的双脉冲测试app可以快捷地实现双脉冲信号设置。

AFG31000系列任意波函数发生器,双脉冲测试app界面

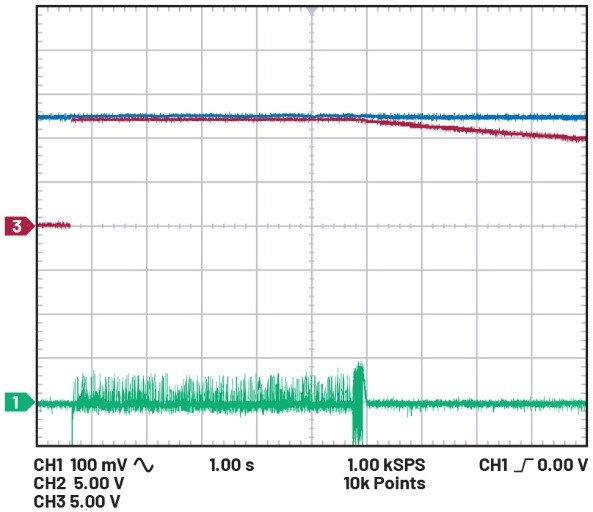

示波器

示波器用于被测器件开关过程波形的采集,至少包含驱动波形、端电压波形和端电流波形,故可以选择4通道示波器。此外,又是需要同时对上下管器件进行测试,这时就可以选择8通道示波器,可以轻松搞定多路信号的采集。

在示波器选择时,还需要考虑其带宽、分辨率、噪声、采样率等。传统的器件开关速度慢,对示波器的要求不高。但随着越来越多先进功率器件的出现,其电压电流范围更广、开关速度更快,对用于双脉冲测试的示波器提出了更高的要求。

示波器可以选择泰克的MSO5B和MSO6B系列示波器的1GHz版本,能够满足高开关速度对带宽的要求,其具有12bit ADC可显著提高测量精度、降低测量噪声,特别对高压大电流器件效果最为显著。此外,MSO5B和MSO6B系列示波器提供4通道、6通道、8通道3种配置选择。

泰克MSO5B系列高分辨率多通道示波器,泰克MSO6B系列高分辨率低噪声示波器

电压探头

电压探头用于测量被测器件的驱动电压波形和端电压波形。

10倍无源探头:带宽高可达1GHz、衰减倍数小,使用无源探头能够获得精准的驱动电压波形。由于其属于无源探头,故仅能用于测量下管器件的驱动电压。同时还可用于200V以下器件端电压测量,能够获的最精准的端电压测量结果。在使用时同样需要注意接地线的影响和阻抗匹配问题,且只能用于下管测量。在使用10倍无源探头测量驱动电压时,需要注意接地线的影响和阻抗匹配。

泰克10X无源探头

高压单端探头:最高测量范围高达2500V,最高带宽可达800MHz,能够获的最精准的端电压测量结果。在使用时同样需要注意接地线的影响和阻抗匹配问题,且只能用于下管测量。

泰克高压单端探头

高压差分探头:其为差分输入,故可以用于上管测试,但由于其CMRR不够高,其测量结果正确性和精度不足以用于精准的器件特性分析;属于有源探头,输入阻抗相比10倍无源探头更大,当被测器件发生损坏时,对示波器来讲更加安全;由于其衰减倍数较大,一般在50倍以上,导致其测量的驱动电压波形上噪声较大、精度较低;由于其端部接线长度较长,容易受到干扰,导致测量结果错误。

泰克高压差分探头

光隔离探头:带宽高可达1GHz,最小衰减比仅1倍,1GHz下CMRR高达-90dB,使用光隔离探头能够获得最准确的驱动电压波形,是现阶段测量上管驱动电压波形的最佳工具。

泰克光隔离探头TIVP

电流探头

罗氏线圈:测量范围从几十A到几千安无饱和问题,只能测量交流电流,无法测量直流电流,正好可以用于测量器件开关/反向恢复特性。罗氏线圈正好套入器件中测量电流,如分立器件的引脚、功率模块的端子、功率模块的键合线,这样的方式不会破坏主功率线路而对器件特性造成影响。但其最高带宽仅为30MHz,无法精准测量高速器件的电流。

泰克罗氏线圈

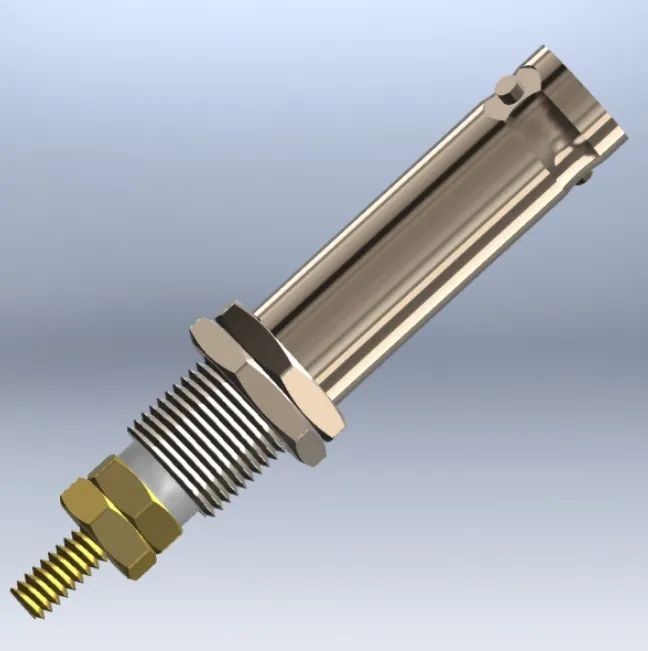

同轴电阻:最大带宽可达1GHz以上,特殊安装方式引入功率回路的寄生电感较小,测量精度高,能够获得精准的器件断电流,特别对SiC、GaN器件更是不二之选。

泰克与系统商一同完美实现搭建双脉冲平台系统——DPT1000A 功率器件动态参数测试系统,专门用于针对三代半导体功率器件的动态特性分析测试,解决客户在功率器件动态特性表征中常见的疑难问题。

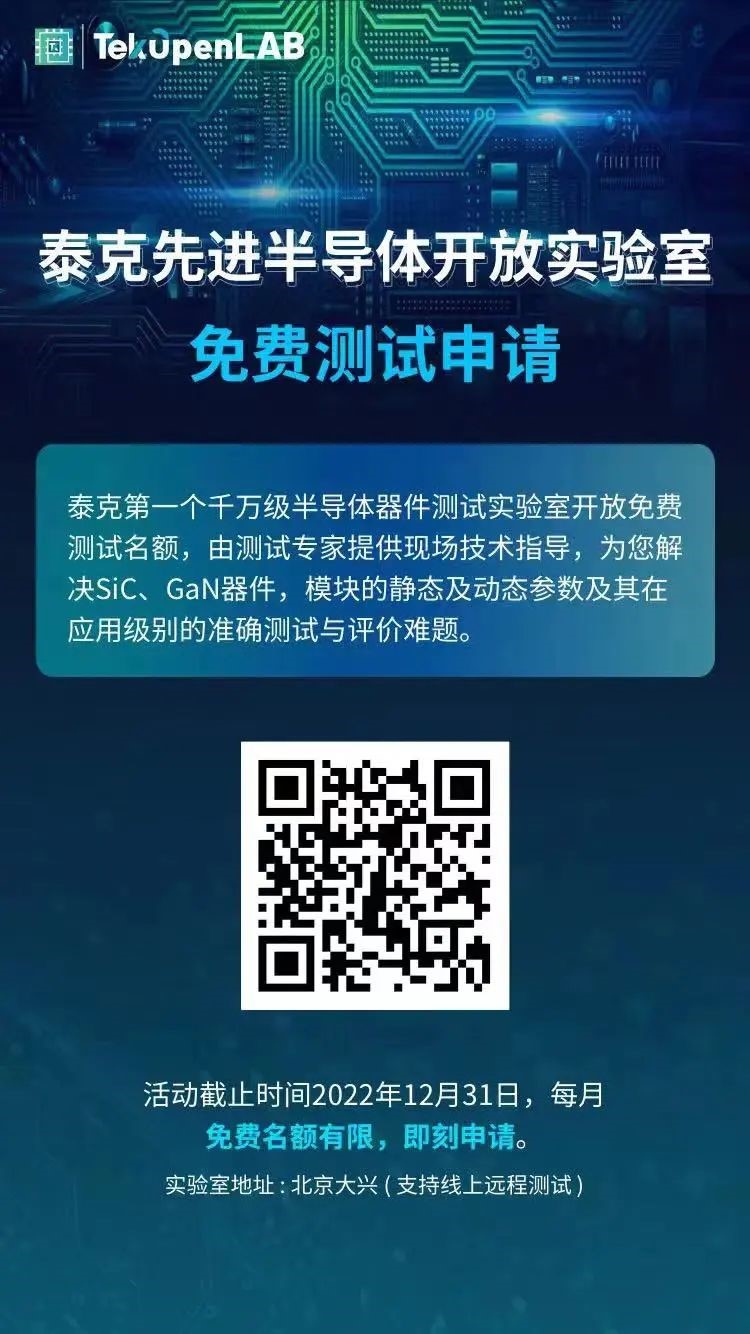

该系统亮相在泰克第三代半导体测试开放实验室。该实验室是泰克第一个千万级半导体器件测试实验室,已经开放免费测试名额,将由测试专家提供现场技术指导,为您解决SiC和GaN器件在模块的静态及动态参数、在应用级别的准确测试与评价难题。

如果你想评估第三代半导体器件性能,如果你想验证所选功率器件是不是符合您的产品设计要求,那就来预约泰克先进半导体开放实验室吧!专家指导,精确评估,让您使用无忧!

内容来源:功率器件显微镜

关于泰克科技

泰克公司总部位于美国俄勒冈州毕佛顿市,致力提供创新、精确、操作简便的测试、测量和监测解决方案,解决各种问题,释放洞察力,推动创新能力。70多年来,泰克一直走在数字时代前沿。欢迎加入我们的创新之旅,敬请登录:tek.com.cn