作者:电子创新网张国斌

在上周的第五届RISC-V中国峰会上,很多EDA公司都宣布了是对RISC-V的支持,同样是设计一款芯片,设计一款RISC-V处理器与设计一款ARM处理器,在EDA工具支持上有哪些不同?老张通过查找资料做了一些汇总,原来设计一款 RISC-V 处理器与设计一款 ARM 处理器,在 EDA 工具支持层面存在较明显的生态差异、工具链可用性、IP配套性、软件支持性等不同。下面从多个维度进行对比分析:

一、授权模式与开发起点差异

结果: 设计RISC-V处理器需从架构定义、ISA配置、仿真验证做起,对EDA的自定义与底层建模能力要求更高。一个形象地比喻是设计ARM处理器像用预制菜做宴席,全套半成品送到厨房;设计RISC-V更像从种菜开始,但能自由调配口味。

二、EDA工具链适配度对比

1. 前端设计(RTL设计、仿真、功能验证)

结论: ARM因IP商业化程度高,验证流程标准化;RISC-V设计需开发者具备更多EDA适配能力。

2. 后端实现(综合、时序、DFT、物理实现)

结论: ARM处理器后端设计路径清晰,EDA工具已有大量“预配置”;RISC-V自由度高但更依赖自定义EDA工具链能力。

3. 形式验证 & 功能等价检查

ARM:大厂提供Golden Reference Model,EDA工具(如Formality)可直接验证。

RISC-V:需自建或使用开源ISA Model(如Spike),验证流程复杂度提升。

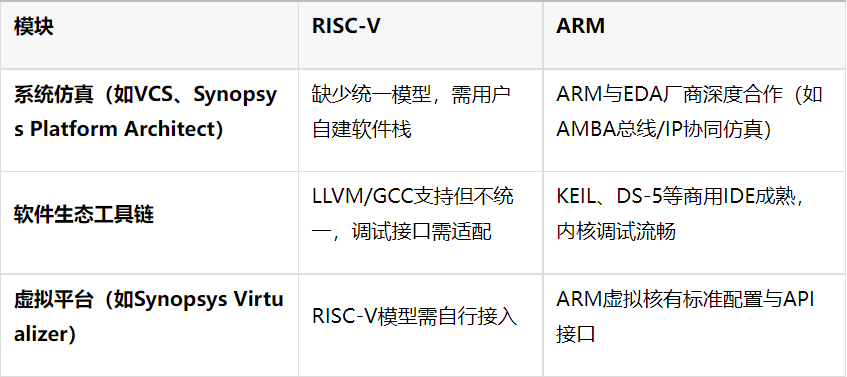

三、软硬协同与系统仿真支持差异

四、IP接口与系统集成支持差异

五、实际产业开发经验差异

六、总结:EDA层面的RISC-V vs ARM对比

结语:

RISC-V设计在EDA工具层面更自由,但也更挑战;ARM设计生态更封闭,但EDA工具更成熟。

从这次峰会看,EDA厂商正逐步增强对RISC-V的支持(如Cadence推出RISC-V验证平台、Synopsys支持RISC-V仿真模型),但当前RISC-V设计团队仍需具备更强的工具链适配与软硬协同能力。

以上是一些总结,如有遗漏欢迎补充!

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利