近年来,因为新能源汽车、光伏及储能、各种电源应用等下游市场的驱动,碳化硅功率器件取得了长足发展。更快的开关速度,更好的温度特性使得系统损耗大幅降低,效率提升,体积减小,从而实现变换器的高效高功率密度化。但是,像碳化硅这样的宽带隙(WBG)器件也给应用研发带来了设计挑战,因而业界对于碳化硅 MOSFET平面栅和沟槽栅的选择和权衡以及其浪涌电流、短路能力、栅极可靠性等仍心存疑虑。

碳化硅MOSFET性能如何?

650V-1200V电压等级的SiC MOSFET商业产品已经从Gen 2发展到了Gen 3,随着技术的发展,元胞宽度持续减小,比导通电阻持续降低,器件性能超越Si器件,浪涌电流、短路能力、栅氧可靠性等可靠性问题备受关注。那么SiC MOSFET体二极管能抗多大的浪涌电流?其短路能力如何?如何保证栅极可靠性?

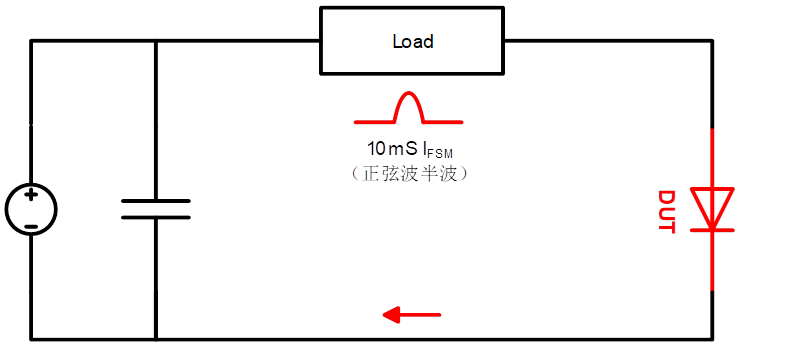

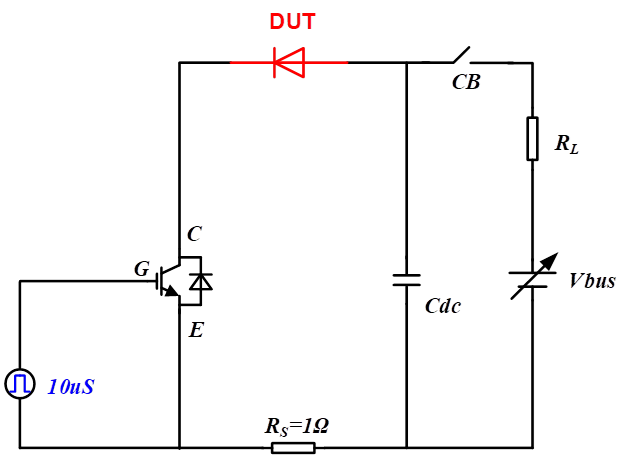

SiC MOSFET的体二极管抗浪涌电流大小与芯片的大小成正比。像派恩杰半导体采用自己搭建的10ms正弦半波浪涌极限测试平台和10us方波半波浪涌极限测试平台对其1200V的SiC MOSFET P3M12080K3进行抽样测试10ms IFSM >120A, 10us IFSM>1100A。

图1 10ms浪涌极限测试平台

图2 10us浪涌极限测试平台

至于短路能力,相较与Si IGBT,SiC MOSFET电流密度更高且栅极氧化层较薄,其短路能力要弱于Si IGBT,但其依然有一定的短路能力。

下表是派恩杰半导体部分产品短路能力:

表1 1200V/650V MOSFET器件短路耐量

No. | Value | Unit | Test Condition |

P3M12017K4 | 3.4 | μS | VDS = 800V, Rgon = 8.2Ω, Rgon = 7.5Ω, Vgs = -5/20V, Tj = 25℃ |

P3M12025K4 | 3.4 | μS | VDS = 800V, Rgon = 8.2Ω, Rgon = 7.5Ω, Vgs = -3/15V, Tj = 25℃ |

P3M12080K4 | 3.0 | μS | VDS = 800V, Rgon = 8.2Ω, Rgon = 7.5Ω, Vgs = -3/15V, Tj = 25℃ |

P3M06060K4 | 6.0 | μS | VDS = 400V, Rgon = 8.2Ω, Rgon = 7.5Ω, Vgs = -3/15V, Tj = 25℃ |

派恩杰半导体针对栅极的可靠性是严格按照AEC-Q101标准进行,在栅极分别加负压和正压(-4V/+15V)温度175℃下进行HTGBR和HTRB实验1000h无产品失效。除了常规AEC-Q101中要求的1000h小时实验,派恩杰半导体对于栅极寿命经行了大量研究。由于SiC/SiO2界面存在比Si/SiO2更大数量级的杂质缺陷,因此SiC MOSFET通常拥有更高的早期失效概率。为了提高SiC MOSFET的栅极可靠性,通过筛选识别并出早期失效非常重要。派恩杰半导体通过TDDB实验建立栅氧加速模型并建立筛选机制来消除潜在的失效可能性器件(可见往期推送)。

除了TDDB外,当正常器件使用时,由于半导体-氧化界面处缺陷的产生或充放电,SiC MOSFET的阈值电压会有漂移现象,阈值电压的漂移可能对器件长期运行产生明显影响。派恩杰半导体在高温条件下给SiC MOSFET施加恒定的DC偏压,观察其阈值电压的变化量。一般施加正向偏压应力时,阈值电压向更高的电压偏移;施加负向偏压应力时,阈值电压向更低的电压偏移。这种效应是由于SiC/SiO2界面处或附近的载流子捕获引起的,负向高压是MOS界面附近的空穴被俘获,产生更多的空穴陷阱;相反正向高压造成电子的俘获。 当然,也有的竞品产品在施加正向偏压应力时,阈值电压向更低的电压偏移;施加负向偏压应力时,阈值电压向更高的电压偏移。这是由于可移动离子在SiC/SiO2界面积累造成的,正向的偏压使得正性的可移动离子在SiO2/SiC界面积累,造成阈值电压负向漂移;负向的偏压使得正性的可移动离子在poly/SiO2界面积累,造成阈值电压正偏。为评估器件在使用过程中阈值电压漂移情况,派恩杰半导体进行了大量BTI实验,基于实验数据建立了PBTI&NBTI模型,借助模型可知晓器件在不同温度和栅压情况下的阈值电压漂移程度。以P3M12080K4产品为例,该产品在极端应用情况下(PBTI:Vgs=19V,TA=150℃)使用20年阈值电压的漂移情况(+0.348V),该产品在极端应用情况下(NBTI:Vgs=-8V,TA=150℃)使用20年阈值电压的漂移情况(-0.17V)。

Cascode、平面栅、沟槽栅优缺点

为提高高压电源系统能源效率,半导体业者无不积极研发经济型高性能碳化硅功率器件,例如Cascode结构、碳化硅MOSFET平面栅结构、碳化硅MOSFET沟槽栅结构等。这些不同的技术对于碳化硅功率器件应用到底有什么影响,该如何选择呢?

首先,Cascode是指采用Si MOSFET和常开型的SiC JFET串联连接,如图3所示。当Si MOSFET栅极为高电平时,MOSFET导通使得SiC JFET的GS短路,从而使其导通。当Si MOSFET栅极为低电平时,其漏极电压上升直至使SiC JFET的GS电压达到其关断的负压时,这时器件关断。Cascode结构主要的优点是相同的导通电阻有更小的芯片面积,由于栅极开关由Si MOSFET控制,使得客户在应用中可以沿用Si的驱动设计,不需要单独设计驱动电路。

图3 SiC Cascode结构示意图

派恩杰半导体认为,Cascode结构只是从Si产品转向SiC产品的一个过渡产品,因为Cascode结构完全无法发挥出SiC器件的独特优势。首先,由于集成了Si MOSFET限制了Cascode的高温应用,特别是其高温Rdson会达到常温下的2倍;其次,器件开关是由Si MOSFET控制,因此开关频率远低于正常SiC MOSFET器件,这是由于JFET和Si MOSFET的合封其dv/dt也只能达到10V/ns 以下,而SiC MOSFET的dv/dt通常可以到达30V/ns~80V/ns。这些缺点使得Cascode也无法减小无源元件的尺寸,从而达到减小整体系统体积和成本的需求;最后,虽然从Cascode结构上是由SiC 高压JFET器件来承受母线电压,但是在开关过程中,MOSFET和JFET的输出电容依然会分压,当回路中存在电压震荡时,低压Si MOSFET依然有被击穿的风险。

SiC MOSFET沟槽栅的主要优势来源于纵向沟道,这不但提高了载流子迁移率(这是由于SiC(11![]() )晶面的迁移率高于(0001)晶面)而且可以缩小元胞尺寸从而有比平面型MOSFET更低的比导通电阻。然而,由于SiC非常坚硬,想要获得均匀,光滑且垂直的刻蚀表面的工艺难度和控制要求都非常的高,这也是只有英飞凌和Rohm推出沟槽栅SiC MOSFET的原因。沟槽栅工艺不仅对工艺实现要求非常高,在可靠性方面也存在一定的风险。首先,由于沟槽刻蚀后表面粗糙度和角度的限制使得沟槽栅的栅氧质量存在风险;其次,由于SiC的各向异性,沟槽侧壁的氧化层厚度和沟槽底部的氧化层厚度不同,因此必须采用特殊的结构和工艺来避免沟槽底部特别是拐角部分的击穿,这也增加了沟槽栅栅氧可靠性的不确定性;最后,由于trench MOSFET的结构,使得trench栅氧的电场强度要高于平面型,这也是Infineon和Rohm要做单边和双沟槽的原因。

)晶面的迁移率高于(0001)晶面)而且可以缩小元胞尺寸从而有比平面型MOSFET更低的比导通电阻。然而,由于SiC非常坚硬,想要获得均匀,光滑且垂直的刻蚀表面的工艺难度和控制要求都非常的高,这也是只有英飞凌和Rohm推出沟槽栅SiC MOSFET的原因。沟槽栅工艺不仅对工艺实现要求非常高,在可靠性方面也存在一定的风险。首先,由于沟槽刻蚀后表面粗糙度和角度的限制使得沟槽栅的栅氧质量存在风险;其次,由于SiC的各向异性,沟槽侧壁的氧化层厚度和沟槽底部的氧化层厚度不同,因此必须采用特殊的结构和工艺来避免沟槽底部特别是拐角部分的击穿,这也增加了沟槽栅栅氧可靠性的不确定性;最后,由于trench MOSFET的结构,使得trench栅氧的电场强度要高于平面型,这也是Infineon和Rohm要做单边和双沟槽的原因。

SiC MOSFET平面栅则是最早也是应用最广泛的结构,目前主流的产品均使用该结构。派恩杰半导体产品采用的是也是平面栅MOSFET结构。基于平面栅结构,派恩杰已经发布了650V-1700V各个电压平台的SiC MOSFET,而且已经顺利在新能源龙头企业批量供货,实现“上车”。