作者:电子创新网张国斌

在人工智能加速发展的今天,通过大语言模型设计一款芯片已经不再是天方夜谭,在7月18日第五届RISC-V中国峰会前沿技术创新论坛上,北京大学集成电路学院助理教授、博雅青年学者贾天宇博士分享了他的团队在“大模型辅助的RISC-V SoC敏捷设计”方向的探索与突破。

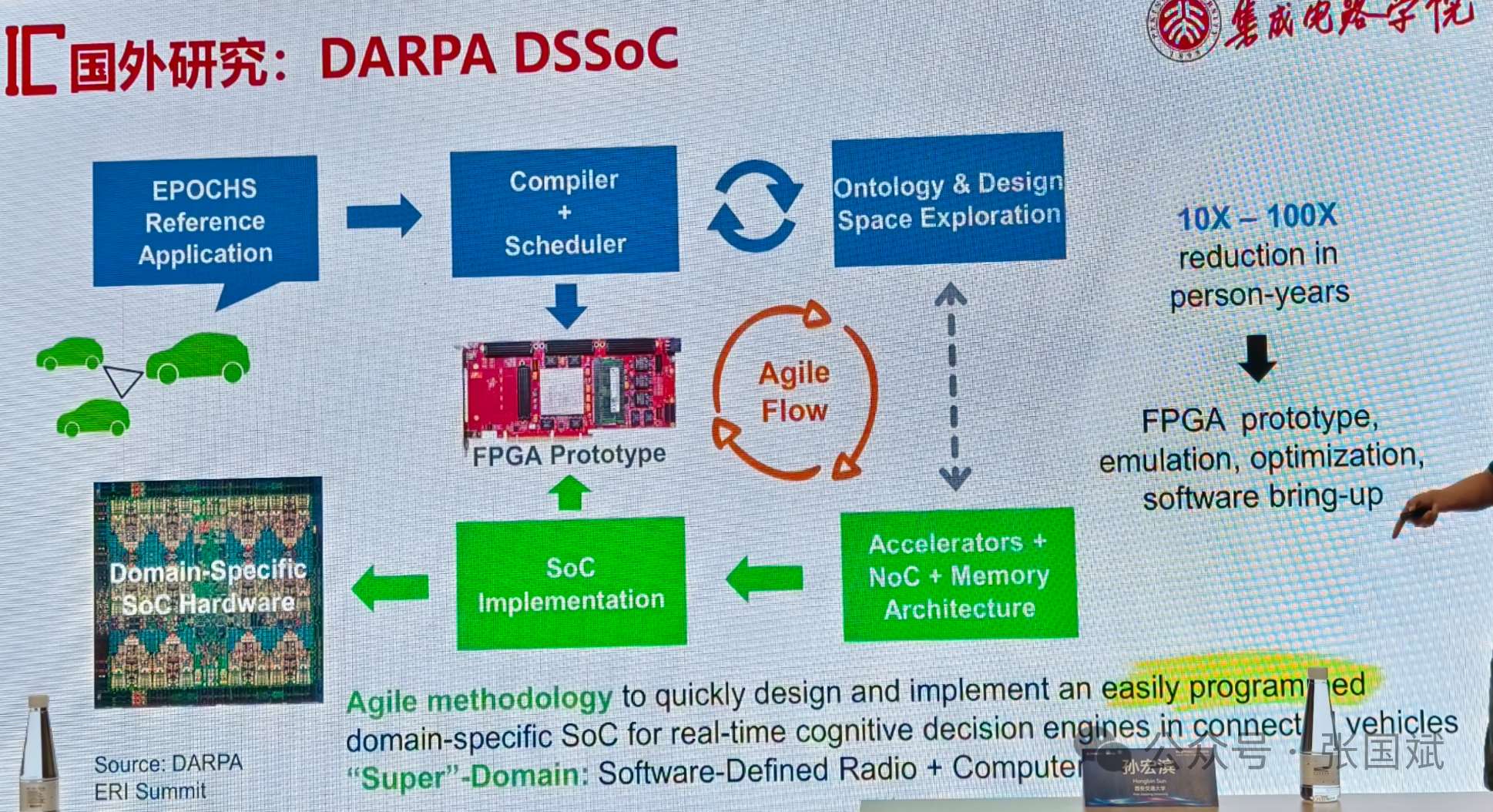

他的报告从Apple A18等商用SoC的高度集成出发,提出:如何利用开源与大语言模型技术,实现SoC芯片的敏捷设计、自动生成与高效验证,是面向未来AI算力平台的关键突破口。

一、SoC设计为何如此复杂?

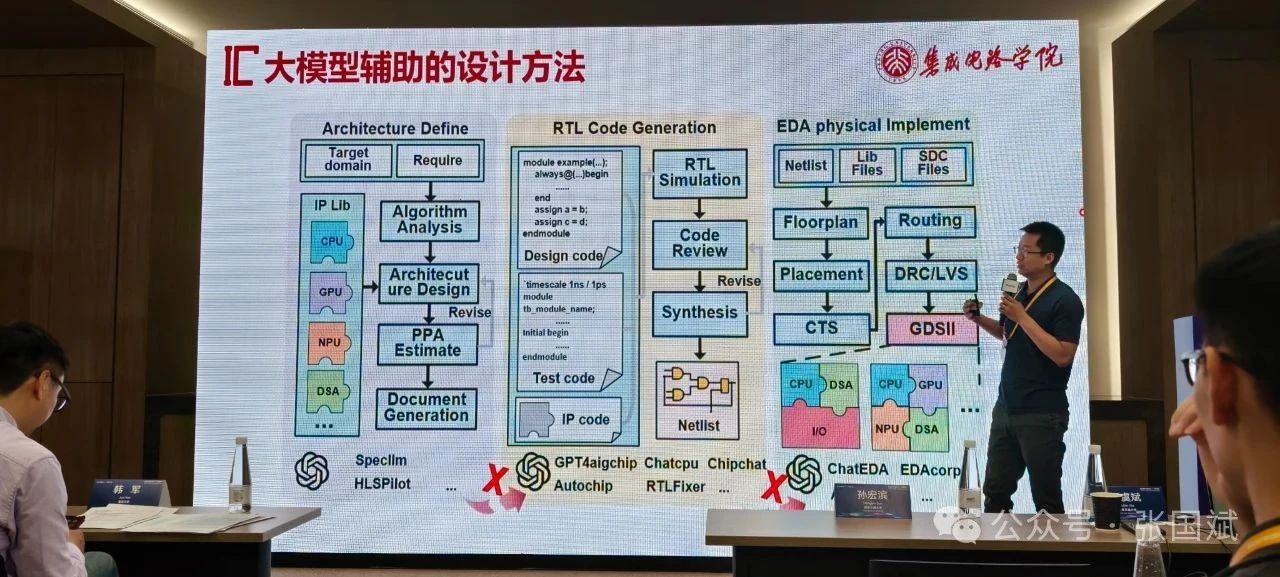

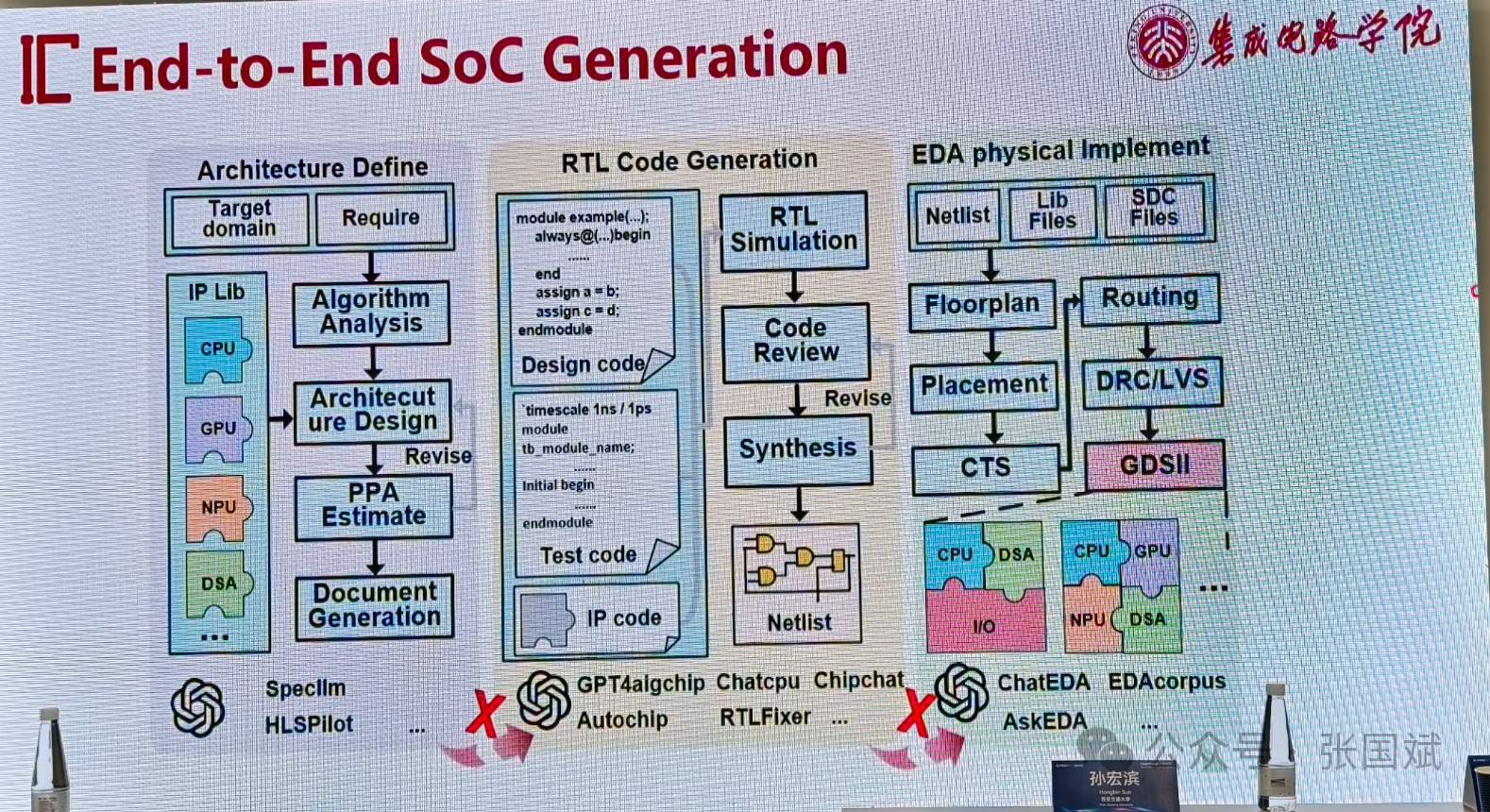

现代SoC芯片集成了CPU、GPU、NPU、AI加速器、DSA(专用结构)以及复杂的片上互联系统。贾博士指出传统的设计流程涉及架构定义与设计空间探索(DSE)、手动 RTL 编码与代码实现、EDA流程、脚本开发、综合、布局布线、验证与物理版图生成等。这些流程需要大量工程师投入,周期长、成本高,设计效率难以满足快速迭代的AI应用需求。

贾教授指出,RISC-V开源架构为SoC设计提供了可重用的构件资源,降低重复开发成本。其团队早在海外期间就探索了基于开源IP实现10-100倍能效优化的设计流程,并延续到当前的大模型辅助研究。

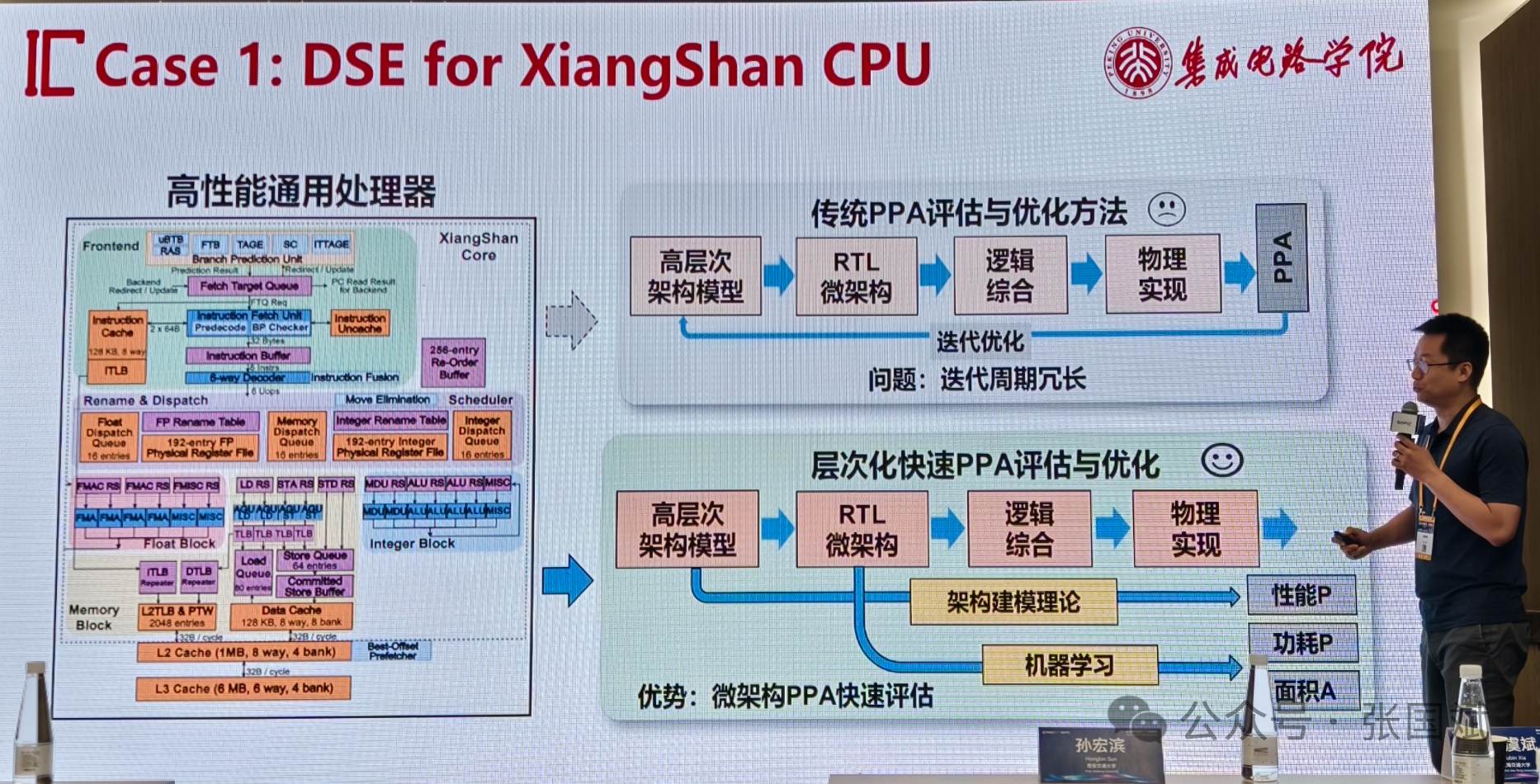

通过以“香山”RISC-V核为基础的仿真器(Gem5),搭建起可拓展的设计空间,实现架构到RTL的全链路流程,为后续引入大模型提供了数据与验证基础。

三、大语言模型赋能SoC敏捷设计的三大路径

贾天宇教授将整个SoC设计流程拆解为三大步骤,并依次引入大语言模型(LLM)进行协同探索:

1. 架构设计空间探索(DSE)

场景: 架构师需评估不同参数组合下的性能与功耗;

方法: 将Gem5仿真结果喂给大模型,提示其分析架构瓶颈,提出优化建议;

结果: 通过对南湖Tace CPU进行发射宽度、解码宽度等参数调整,得到更优帕累托前沿的设计点,物理实现后芯片面积和功耗均下降。

他指出大模型不仅能理解结构参数,还能指导修改,如:“减小解码宽度可节省面积但略微降低性能”,展示出“类架构师”的理解力。

2. 代码生成与集成验证

挑战: 单一模块可生成,但多个IP的复杂集成难以“一步到位”;

方法: 引入RAG(检索增强生成)技术,通过知识检索+大模型生成的组合,构建模块化模板;

应用案例: 给定AI加速器需求,模型能自动生成具有向量扩展功能的协处理器(Co-Processor)架构与代码片段;

他指出模型可以支持将多个IP(如香山CPU、开源DSP、NPU)集成为完整的AI SoC草图设计。

通过RAG方式解决了“复杂结构信息难直接生成”的问题,走向更精细化、可控的设计流程。

3. EDA流程与逻辑综合辅助

虽然EDA阶段目前仍需大量专家手动干预,但贾博士指出,大模型已开始介入脚本编写、综合参数配置、甚至逻辑验证策略的建议生成。他们的目标是实现设计流程的全覆盖与智能闭环。

四、从Demo到产品:LLM辅助芯片设计的挑战与展望

他指出当前大模型能部分接替设计工程师完成参数调优、代码生成、结构分析等任务;在某些环节上显著降低设计复杂度与周期。但也面临幻觉问题(Hallucination),就是生成内容可能逻辑不一致或语义错误,所以生成之后仍需严密的仿真与验证流程闭环;此外,复杂SoC的集成要求模块之间接口与时序严格匹配。贾博士特别强调:“我们不是只让大模型生成,而是生成+验证+反馈再生成,构建类人闭环的协同工作机制。”

五、结语:开源 × 敏捷 × 大模型,开启芯片设计新范式

贾天宇博士的报告展示了一种颠覆传统的SoC设计路径。开源IP提供资源基础,敏捷流程提供组织方法,而大语言模型则注入智能驱动。三者结合,正逐步催生一套全新的、以AI为核心的芯片设计范式。

虽然当前还只是起步阶段,但正如贾教授所说:“我们的Demo离产品还有距离,但这场技术革命已经开始了。”