作者:电子创新网张国斌

在日益复杂的无线通信系统中,如何在工艺受限的环境下实现高性能、低功耗的数字信号处理(DSP)成为芯片架构师面临的重要挑战。在第五届RISC-V中国峰会前沿创新技术分论坛上芯昇科技高级专家、中国移动拔尖人才李高山发表了题为《DSP领域最新RISC-V指令集及DSA在无线领域中的创新应用》的报告,深度解析了RISC-V在DSP领域的演进与专用架构(DSA)在通信应用中的突破性价值。

一、背景:DSP和通信芯片的矛盾

李高山指出随着5G/6G通信标准的推进,无线信号处理计算密集度显著提升,而工艺水平却受制于外部限制,停留在中低端节点。面对标准协议统一、工艺同质化的“双重挤压”,通信芯片厂商在传统架构下难以实现有效差异化。李高山指出,此背景下指令级定制能力更强、架构更开放的RISC-V平台,为通信DSP的创新提供了理想土壤。

二、RISC-V DSP-W:为无线而生的指令集扩展

他表示芯昇科技联合芯来科技共同推动了名为RISC-dsp-W的新一代DSP指令集,它基于RISC-V架构进行深度定制,作为RISC-V基金会RVV SIG筹备中的DSP TG(Task Group)标准候选方案之一。其核心优势体现在以下几点:

1. 增强型定点算术支持

引入饱和(saturation)、摄入(rounding/clipping)等机制;

提供更广的动态范围与更高的精度,适配复杂信号特性。

2. 原生复数运算能力

支持SC16等主流复数数据类型;

内建复数加乘、乘累加等基本操作指令,提升FFT、滤波效率。

3. 数据类型转换优化

实现整数、小数、复数间的快速转换;提供一致性强的硬件加速接口(如SFT指令集族)。

4. 快速非线性函数支持

内建指数、对数、tanh、sigmoid等AI常用激活函数的分段函数实现;

适配AI/DSP混合场景下的高效计算需求。

李高山展示的数据表明,在无线信号处理中,相同硬件资源下RISC-dsp-W可实现RVV架构4~5倍的性能提升,尤其在点积、卷积等核心DSP算子上表现优越。

三、DSA 架构:为定制而生的RISC-V实践

他指出DSA(Domain Specific Architecture)是旨在为特定领域设计出架构级别最优的解决方案。RISC-V的模块化和开放特性与DSA的需求天然契合,为无线通信领域提供了精准突破路径。

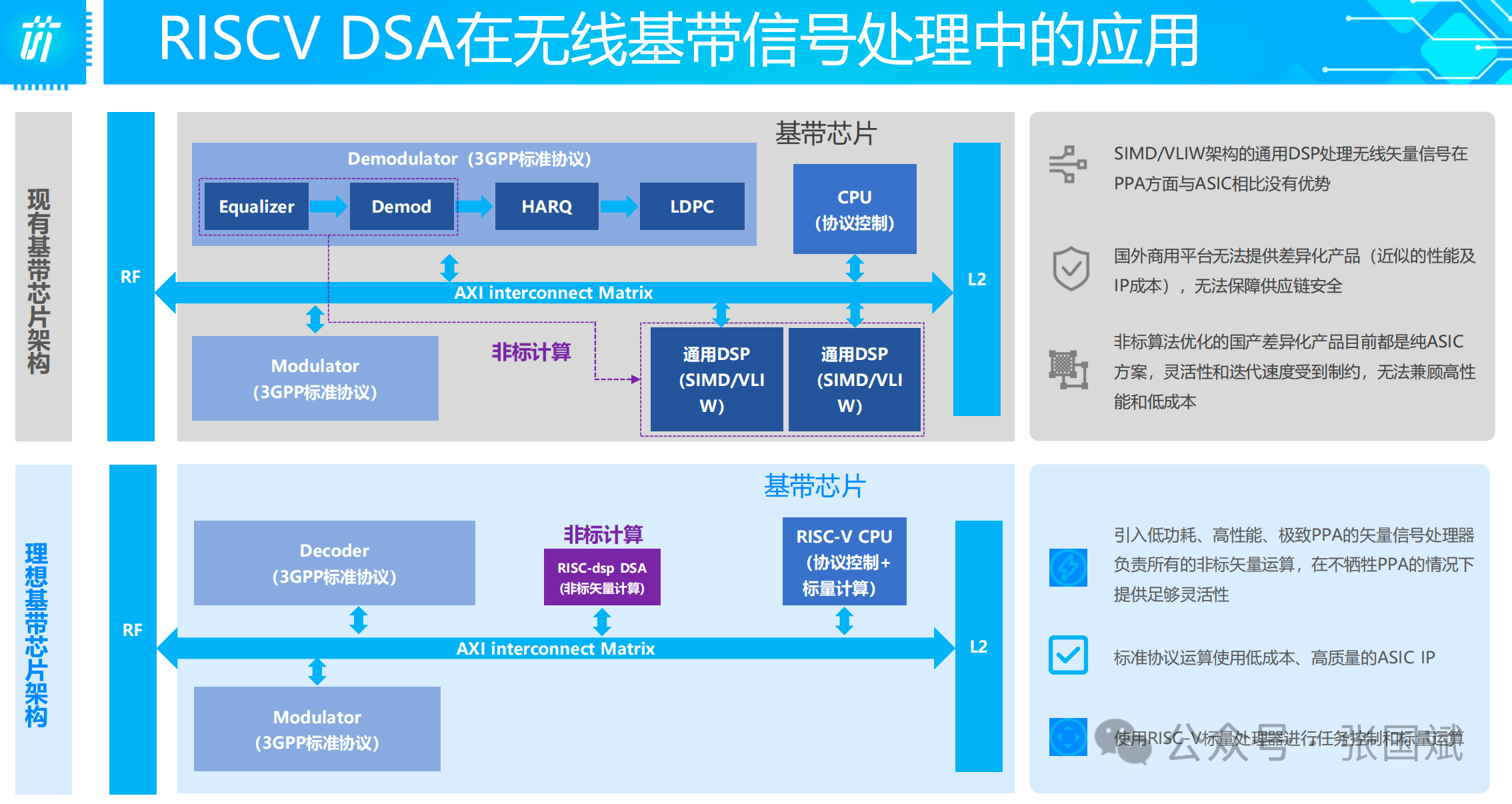

他指出当前基带芯片架构的问题:标准协议固定,无法差异化;通用DSP(如SIMD/VLIW)效率低、功耗高;ACCE类硬件方案缺乏灵活性,只能做低层比拼等。而DSA的突破点则是以RISC-dsp-W为基础构建面向无线信号的定制加速器--面积、功耗与ACCE方案相当,但具备指令级灵活性;还能根据实际场景进行算法、算子级别的优化,更适配非标需求。

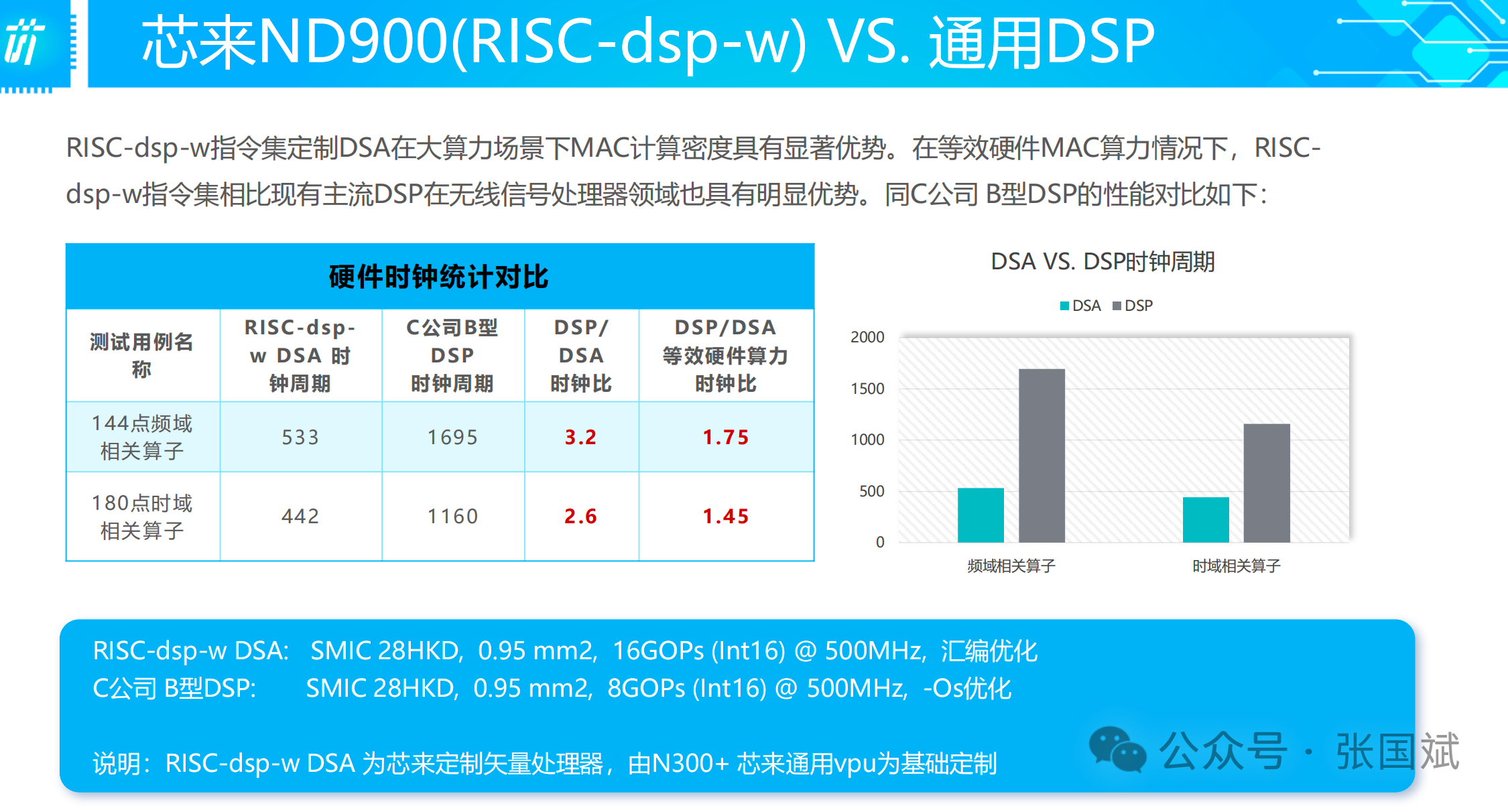

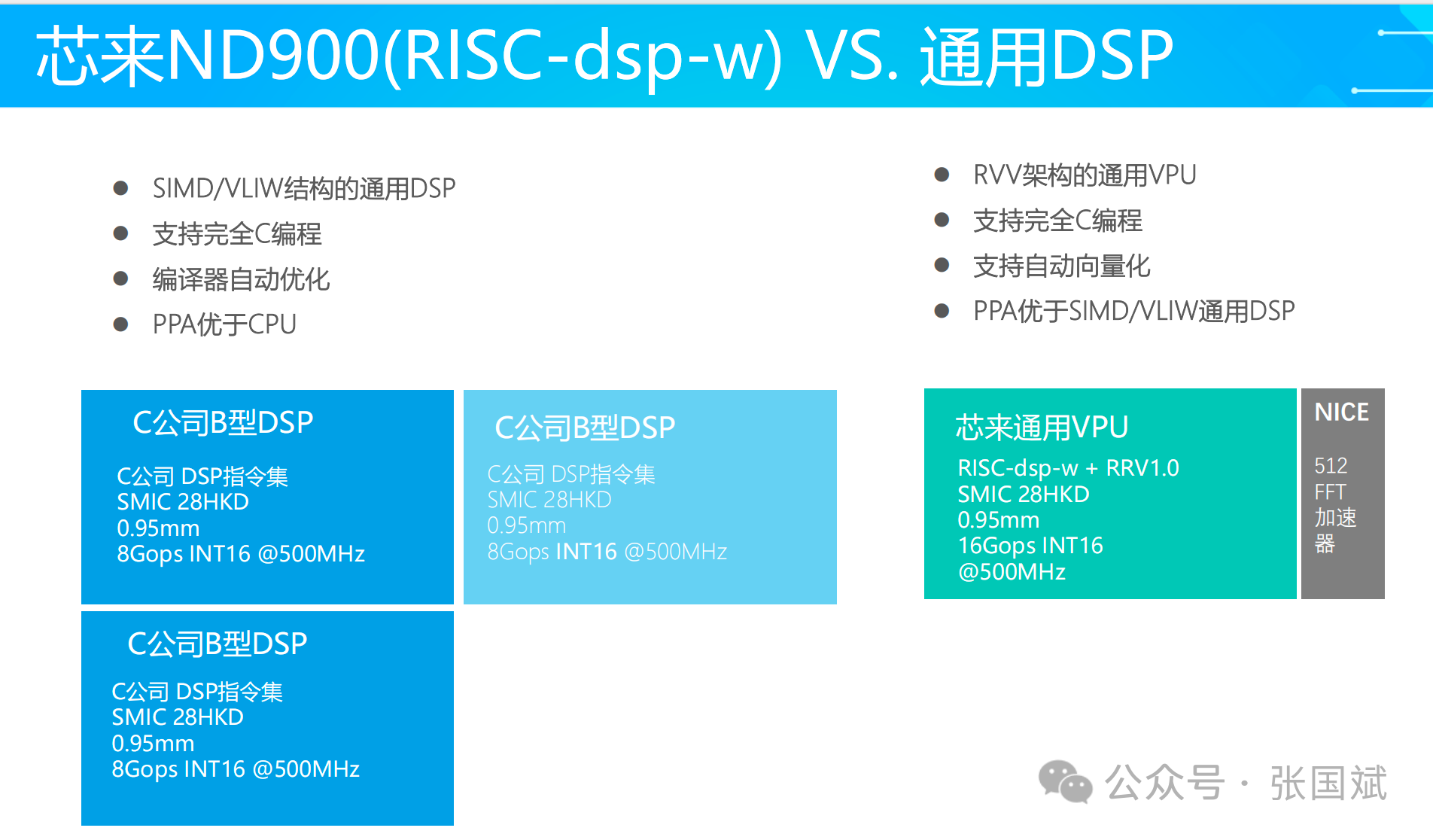

在该架构指导下,芯昇与芯来合作开发的ND900处理器已成为首个支持RISC-dsp-W指令集的DSP核,展现出优于传统DSP在功耗密度、指令效率和灵活性方面的显著优势。

四、自研高性能DSP:释放国产架构潜力

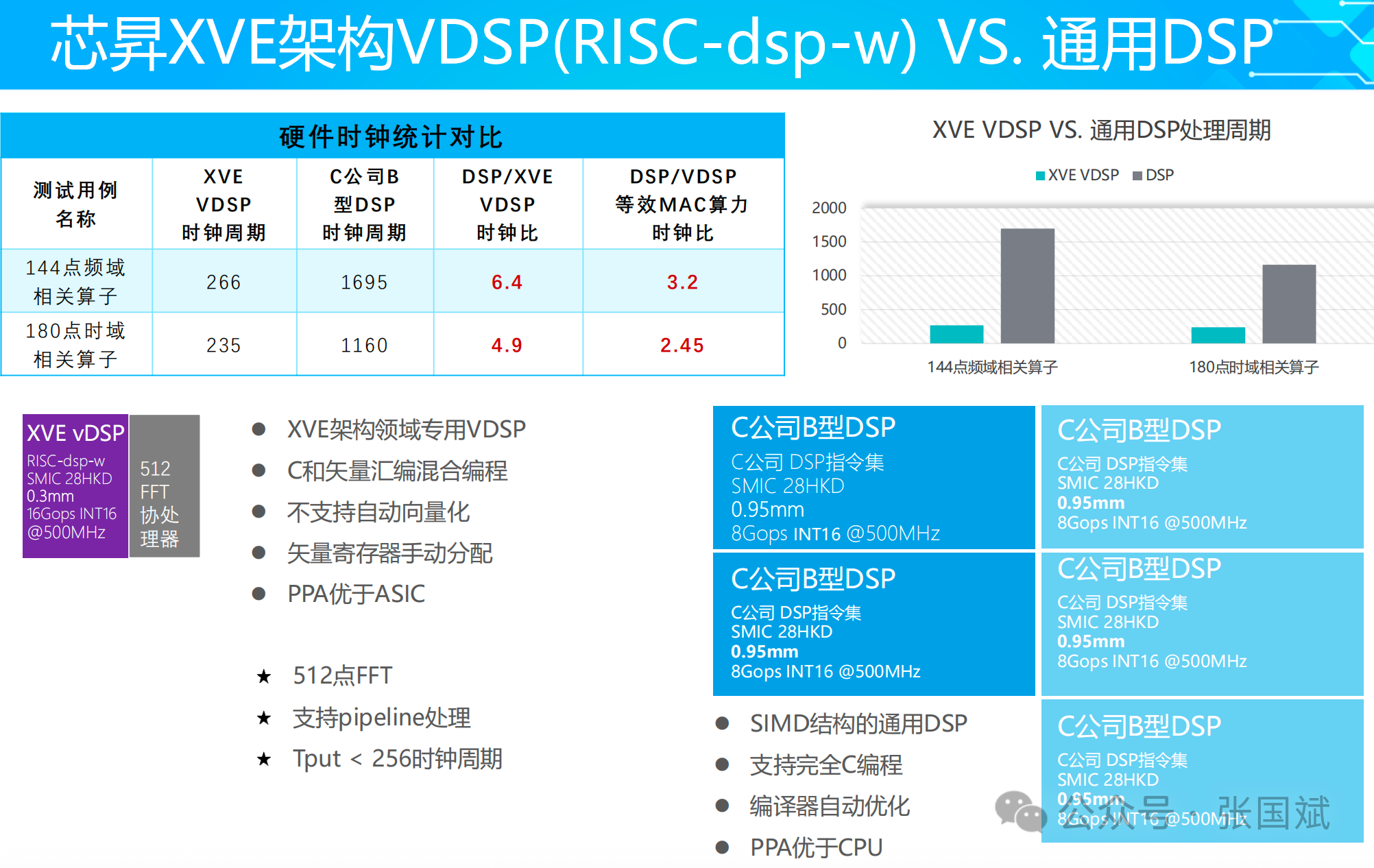

李高山在演讲最后介绍了芯昇最新发布的一款基于RISC-dsp-W的自研DSP架构。其核心特性如下:

混合编程模型:C语言与矢量汇编结合,兼顾易用性与极致性能;

自动向量化适配:针对目标算法可灵活配置VPU(向量处理单元);

高指令效率:同等算力下面积缩小至1/3,功耗显著下降;

设计理念极简主义:去除无用指令与功能单元,最大程度压缩PPA。

正如李高山所比喻:“通用DSP就像轿车,而定制化RISC-V DSP更像赛车——剥离冗余、轻装上阵,目标就是极致的领域性能表现。”

五、RISC-V + DSP + DSA = 通信芯片破局之钥

面对通信芯片“同质化、价格战”的僵局,李高山指出以RISC-V为核心、DSA为方向、RISC-dsp-W为落地载体的架构路径,正为行业提供一条在性能与灵活性之间取得最优平衡的新解法。芯昇科技等头部企业的推进,标志着国产DSP技术在无线通信领域迈向自主可控、高性能发展的关键节点。

作者注:RISC-dsp-W相关标准正在RISC-V基金会的DSP TG中积极推进,未来可能作为Z扩展(如Zvspw)正式发布,预计将对国内外通信与AI芯片设计产生深远影响。建议持续关注该指令集在开源社区和产业界的最新动态。