Richard Oxland , 西门子数字化工业软件 Tessent Embedded Analytics产品经理

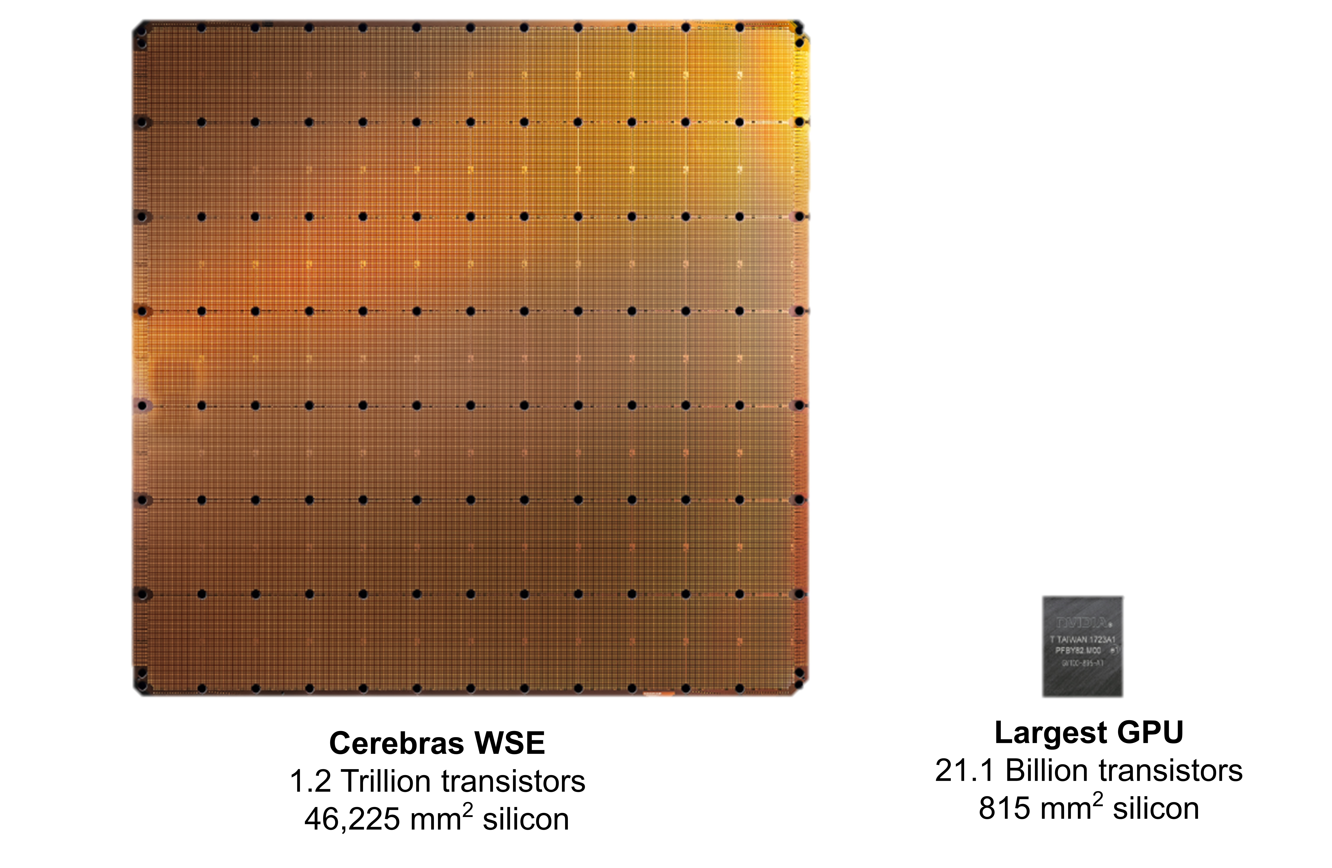

在人工智能和机器学习应用数据处理的强劲需求下,大规模并行计算迅速兴起,导致芯片复杂性呈现爆炸式增长。这种复杂性体现在 Cerebras 晶圆级引擎(如下图)等设计中,该设计是一种平铺多核、多晶片设计,将晶体管数量增加至数万亿个,拥有近百万个计算内核。

人工智能 (AI) SoC 的市场持续增长,竞争也日趋激烈。半导体公司根据性能、成本和灵活性,来找到自己的定位,并不断自我优化,从而导致了新型多核架构的爆发式增长。系统架构师正在尝试不同的方法,希望可以将这种复杂性转化为竞争优势。

在所有复杂性来源中,有一个在多核 AI SoC 中非常重要的来源:即当有多个线程在共享数据上并行运行时,会出现功能错误和性能降低问题。过去,设计人员可以使用经典的 CPU 运行控制来调试问题,但这种方法对多核架构并无效果。导致软件问题的根本原因错综复杂,包括往返时延、内核数量、控制和数据并行、多层层次结构和互相依赖的进程,设计人员从中找出真正根源的机会渺茫。

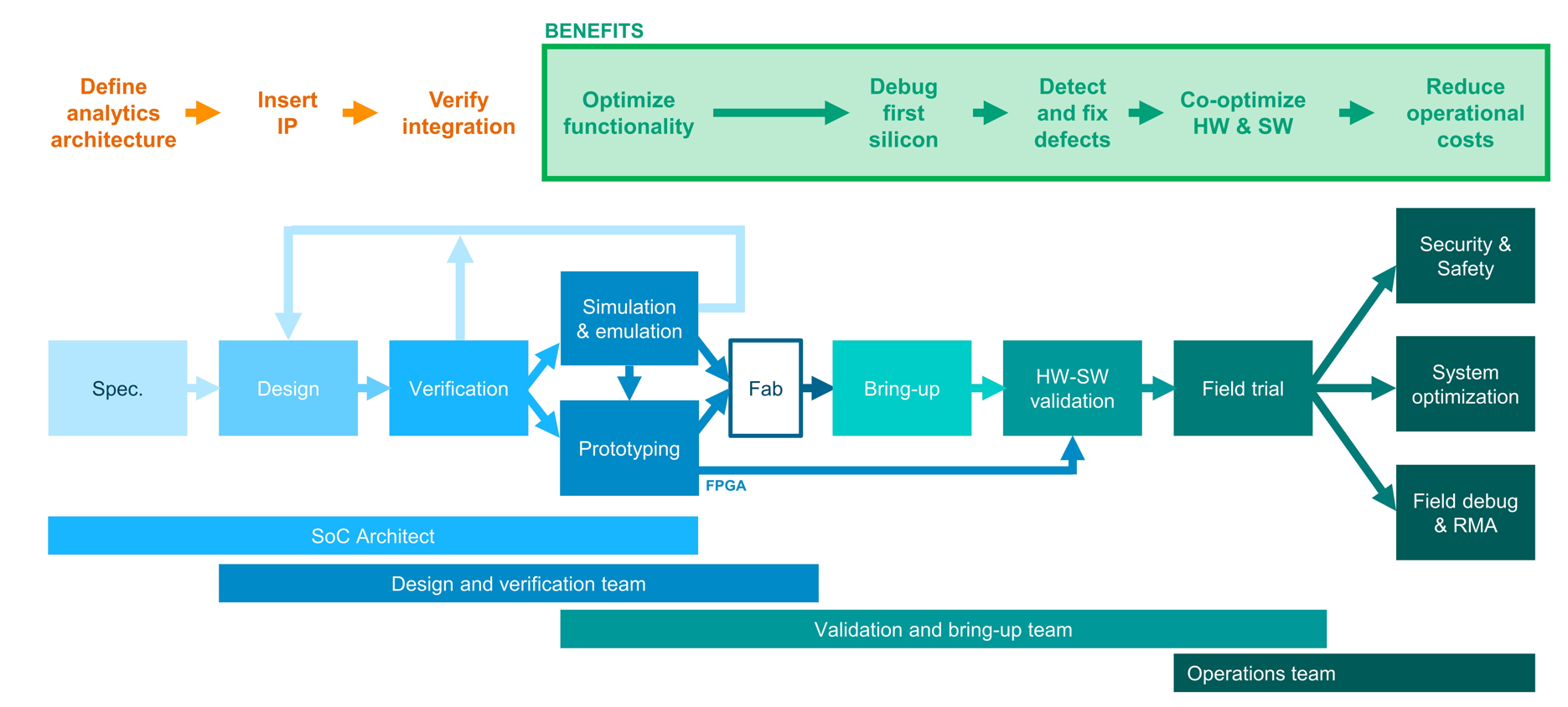

另外,设计人员还需要考虑软硬件协同优化,这需要大量的功能分析。为了在 SoC 上部署 AI 应用,设计人员必须编译源代码,以充分利用多核架构。这通常需要充分了解 SoC 架构的定制工具链。这个过程包括一个硬件和软件优化及测试周期,从 SOC 仿真开始,一直贯穿至第一次投片和后续器件迭代,如下图所示。

通过这一功能分析周期,团队能够了解以下内容:

数据共享的效率;

片上网络 (NoC) 是否超载或不平衡;

如何在不影响代码执行的情况下评估应用性能;

如何优化内存控制器配置文件以提升数据处理能力;

如何关联整个 SoC 中的事件;

要做到这一点,我们需要一种全新的方法来优化 AI SoC 及其上面运行的软件。要将高质量的 AI SoC 及时推向市场并在完成部署后保持性能,必须要进行系统范围的功能分析。系统范围功能分析的部分功能包括:

深入洞察子系统或组件 ;

对整个系统从启动开始的准确、连贯的全景图;

事物感知(Transaction-aware) 的互连监控和统计信息;

传统的处理器运行控制和追踪;

支持所有常见的指令集和互连协议;

提供选择或更改重要子系统的灵活性;

用于产生数据可见性的灵活强大的工具;

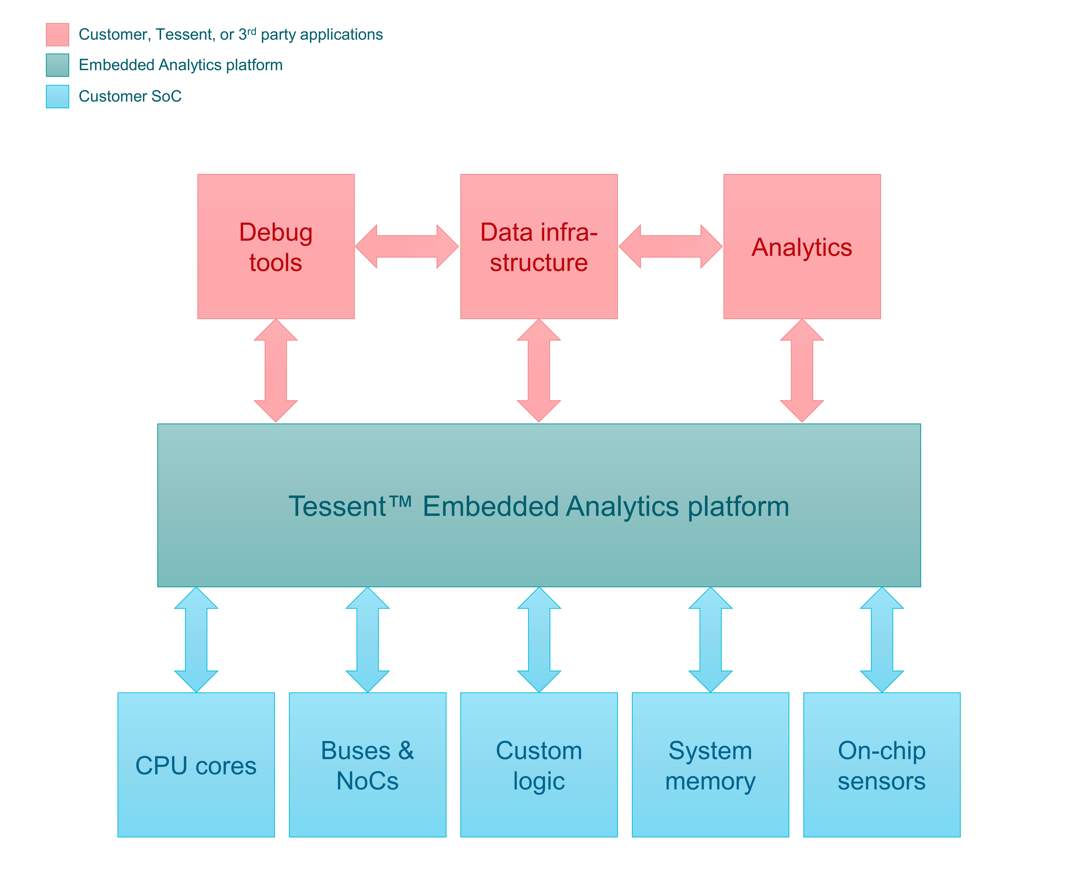

用于监控和分析 IP 的片上基础架构和软件提供了所有这些功能,覆盖范围可从仿真到部署。下图即显示了 SoC 功能监控和分析的典型架构。

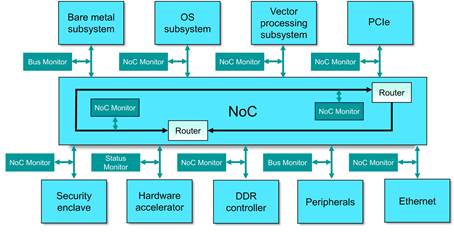

接下来的图中展示的示例是一个多核芯片配备片上网络 (NoC) 监视器,可跟踪所有 NoC 事务到循环缓冲器。由于 NoC 监视器具有事务感知功能,可将其配置为检测特定总线条件,例如导致事务持续时间超过特定阈值(按周期数计算)的死锁。当超过阈值时,NoC 监视器可以输出死锁事务以及之前事务的详细信息,以便对问题进行诊断。

同一个 NoC 监视器也可配置为在检测到相同死锁条件时——例如通过跟踪硬件加速器行为的状态监视器模块——使用嵌入式分析消息基础设施的交叉触发功能,在系统中的其他位置触发跟踪。

了解实施有效的系统验证和优化环境时涉及的问题,是成功交付多核 SoC 的关键,与该领域内的专业供应商合作可实现事半功倍的效果。

如欲了解更多资源,请访问技术论文:利用系统级数据来优化多核 AI 和 ML 芯片