作者:电子创新网张国斌

在RISC-V架构日益复杂、芯片验证压力不断上升的当下,在第五届RISC-V中国峰会上,北京开源芯片研究院、计算所特别研究助理徐易难带来一场极具前瞻性的分享——《SVM:用可综合方法实现RISC-V处理器的高效验证》。这不仅是一场验证技术的技术革命,更是对验证思维范式的重塑。

一、背景:验证成为处理器开发瓶颈

在传统处理器开发中,验证环节始终是资源投入最多、周期最漫长的环节。尽管UVM等高层次验证语言简化了逻辑描述,但其“软硬脱节”的问题始终困扰着业界——尤其在多核、复杂流水线处理器设计如“香山”等平台中,仿真速度之慢严重制约了设计流的高效推进。

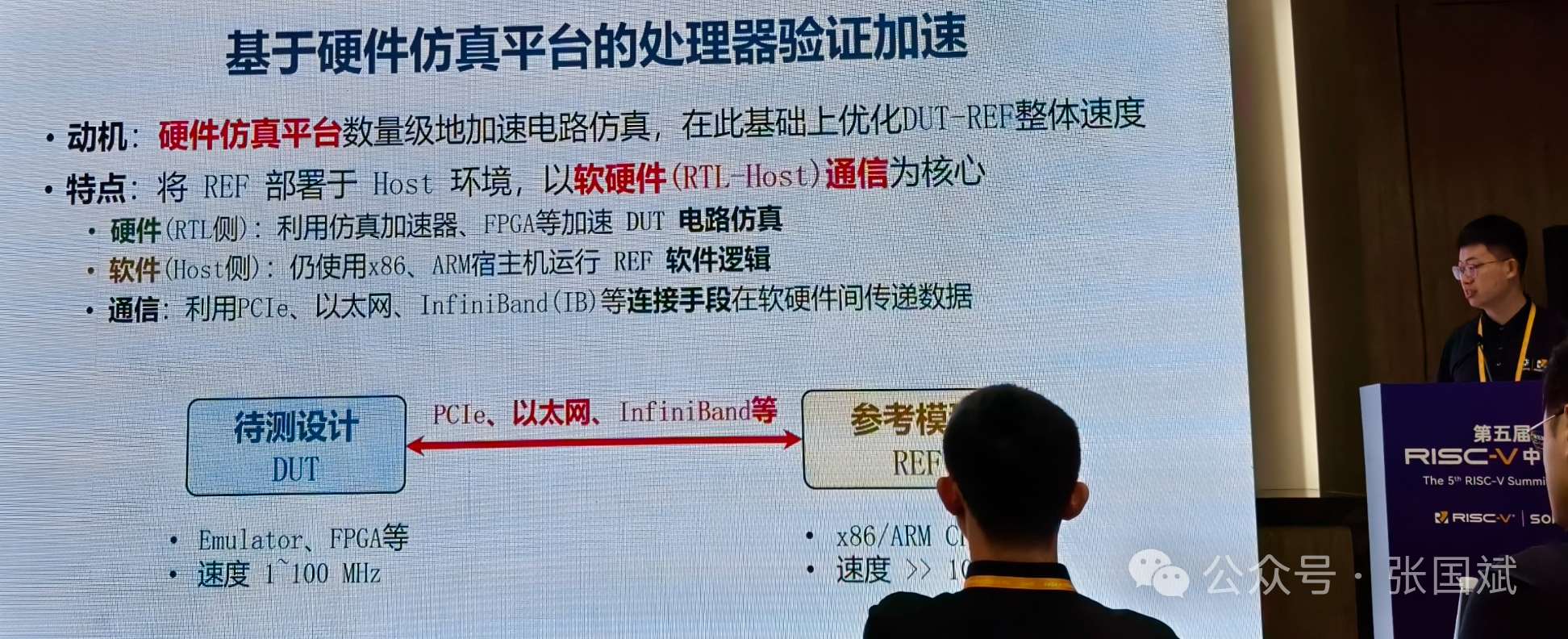

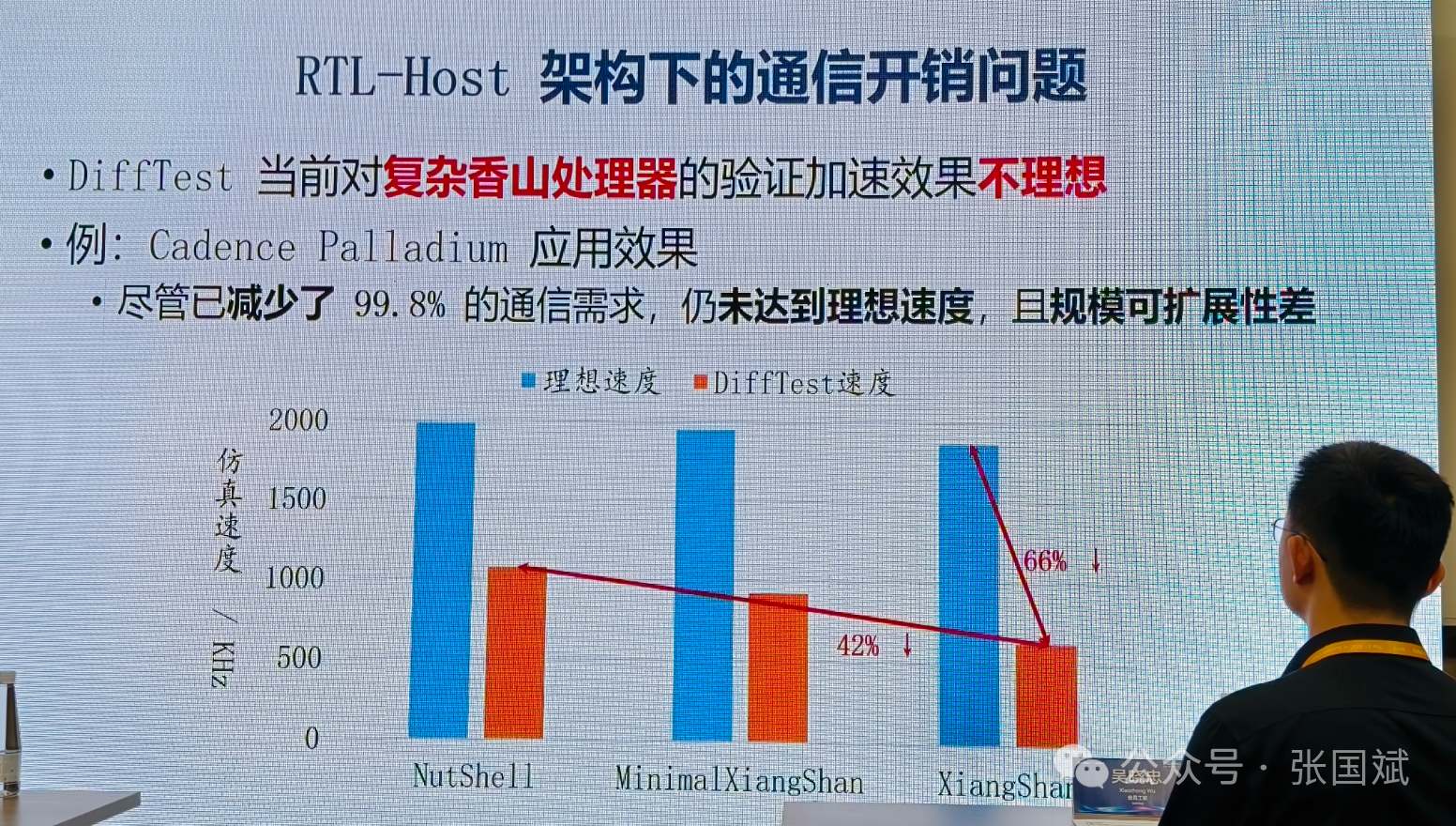

徐易难表示为解决这一矛盾,业界普遍采用“协同仿真”机制(Co-simulation)——通过对比待测设计(DUT)与参考模型(REF)执行结果是否一致来进行验证。但这一框架在转向Emulator或FPGA时,却遭遇了“验证瓶颈”:数据通信频繁、验证速度反而变慢。

二、挑战升级:RISC-V验证难度指数级上升

徐易难指出进入2024年,RISC-V体系结构迎来了重大扩展,RVA23 Profile的出现意味着单一Profile就包含了30多个必选扩展,ISA文档超过800页。这种扩展式复杂性,导致每一种功能、状态和CSR都需独立建模和验证,使得参考模型构建和维护成本骤增。

此外,随着设计复杂度提升,仿真速度持续下降。例如Rocket从单核变为八核,仿真速度下降90%以上,而香山等处理器在FPGA上仿真速度甚至不到1kHz,远无法满足大规模验证需求。

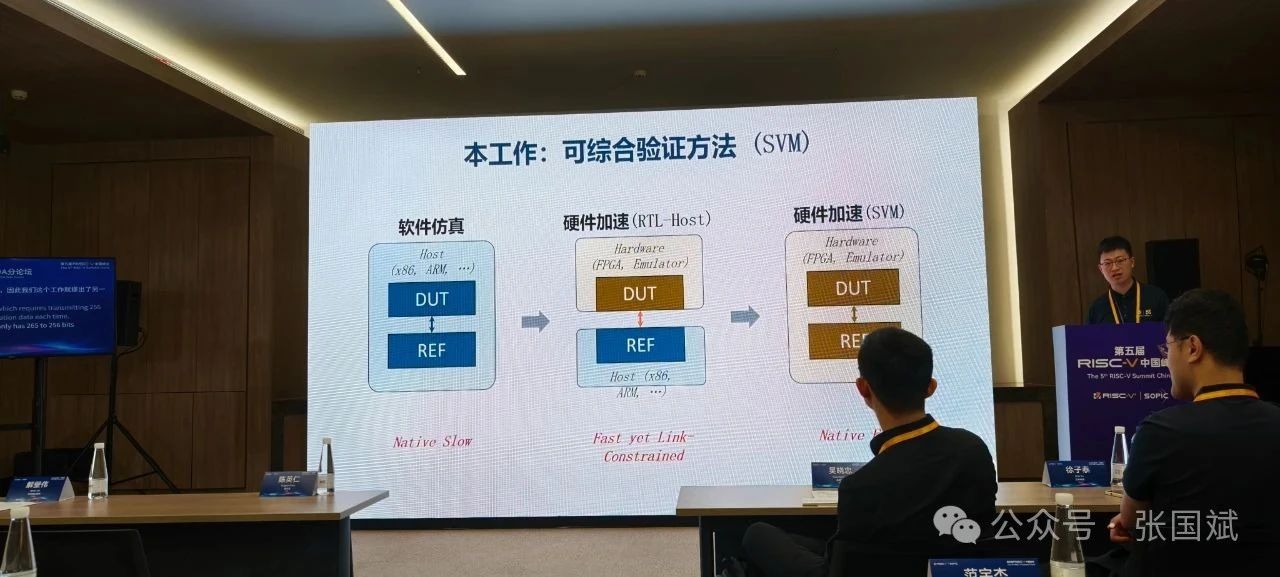

三、SVM:可综合参考模型的提出与创新

徐易难团队提出了SVM(Synthesizable Validation Model)的概念,即将参考模型“硬化”成可综合的RTL模型,并与DUT共同部署于Emulator或FPGA上。这种创新带来了三大技术突破:

1. 参考模型可综合自动生成

团队开发了将Spike等C/C++语义模型自动转换为RTL电路的工具链,自动解析抽象语法树(AST)并转化为Verilog语义结构,有效避免人工转换的冗余和BUG。这一自动迁移系统显著提高了参考模型的可信度和可维护性。

2. 硬件化REF的高效执行架构

在执行效率上,SVM采取了高度精简、无阻塞流水线的设计逻辑,并结合指令预测+Cache同步机制解决控制和数据冒险:

控制冒险:使用DUT的PC预测提前激活REF流水线。

数据冒险:构建片上小Cache,仅保存DUT与REF内存不一致的数据块,实现高速内存访问对齐。

3. 可综合调试机制

考虑到传统调试信息如assert、printf在RTL中难以实现,团队将SVM自身转化为一个“图灵完备的调试CPU”,能够在运行异常后读取片上日志,分析错误源,甚至串口输出错误信息——极大提升了FPGA/Emulator下的可视调试能力。

四、验证性能对比:10倍级提升

在现有DiffTest架构下,Emulator/FPGA验证速度受限于Host间通信(一般仅1MHz)。而SVM框架通过片上直接通信,避免了数据搬运的瓶颈,使FPGA端仿真验证速度提升至60MHz,Emulator端亦可提升至2MHz,与硬件系统的最大处理速度接近,达到了10倍量级的速度增长。

此外,SVM框架对DiffTest原有接口完全兼容,支持香山、果核、RCache等主流RISC-V核,且已经实现部分向量、特权扩展,未来将进一步扩展到更多RISC-V模块。

五、意义与展望:为国产验证工具树立新范式

SVM不仅是一套验证加速工具,更是对整个验证生态的重构:对设计团队而言,它提供了高速验证与全生命周期调试的统一平台;对FPGA/Emu厂商而言,它释放了更大程度的验证资源与价值;对开源社区而言,它为复杂RISC-V核的验证构建起高质量、可维护的底座。

徐易难表示,这套系统已计划在GitHub上开源,并将持续迭代支持更多复杂ISA扩展,为RISC-V处理器验证打造“基础设施级”的支撑平台。

RISC-V的开放性带来了架构灵活的红利,但也加大了验证挑战。SVM正是这一背景下的“硬创新”代表——它突破了UVM范式的上限,用硬件方法解耦性能瓶颈,为国产处理器验证系统化、模块化、高速化奠定了坚实基础。未来,随着SVM与更多Ecosystem(如Perf、调试、仿真)的耦合深化,它有望成为中国芯片产业迈向验证自主、标准可控的新利器。