11月14日,2025年“中国芯”集成电路产业促进大会暨第二十届“中国芯”优秀产品征集结果发布仪式在珠海横琴隆重举办。中国数字EDA/IP龙头企业——上海合见工业软件集团有限公司(简称“合见工软”)凭借全国产UCIe IP解决方案UniVista UCIe IP,成功斩获第二十届“中国芯”优秀支撑服务企业奖项。

在此次会议同期举办的专场论坛上,合见工软市场总监崇华明发表了名为《UCIe IP驱动Chiplet产品快速发展》的主题演讲,深入剖析了国内智算芯片产业面临的挑战,并详细介绍了合见工软UCIe高速接口IP解决方案及优势。

当前,由人工智能、大数据、云计算等技术驱动的智算时代已经到来。智算芯片呈现出高性能、高能效、高内存带宽、高互联总线带宽、大规模设计以及先进封装等特征,对芯片设计提出了更高要求。特别是在当前国际形势下,我国芯片产业在先进制程方面受到较大制约,大算力芯片(高端智算芯片)设计面临技术突破瓶颈。

在此背景下,Chiplet(芯粒技术)成为国产高端芯片破局的关键,通过将大芯片拆分为多个小 “芯粒”(如计算芯粒、存储芯粒),再通过先进封装拼接成完整芯片,从而避免对先进制程的依赖。而UCIe(通用芯粒互联标准)作为Chiplet的统一互联协议,是实现芯粒高效兼容互联的关键路径。

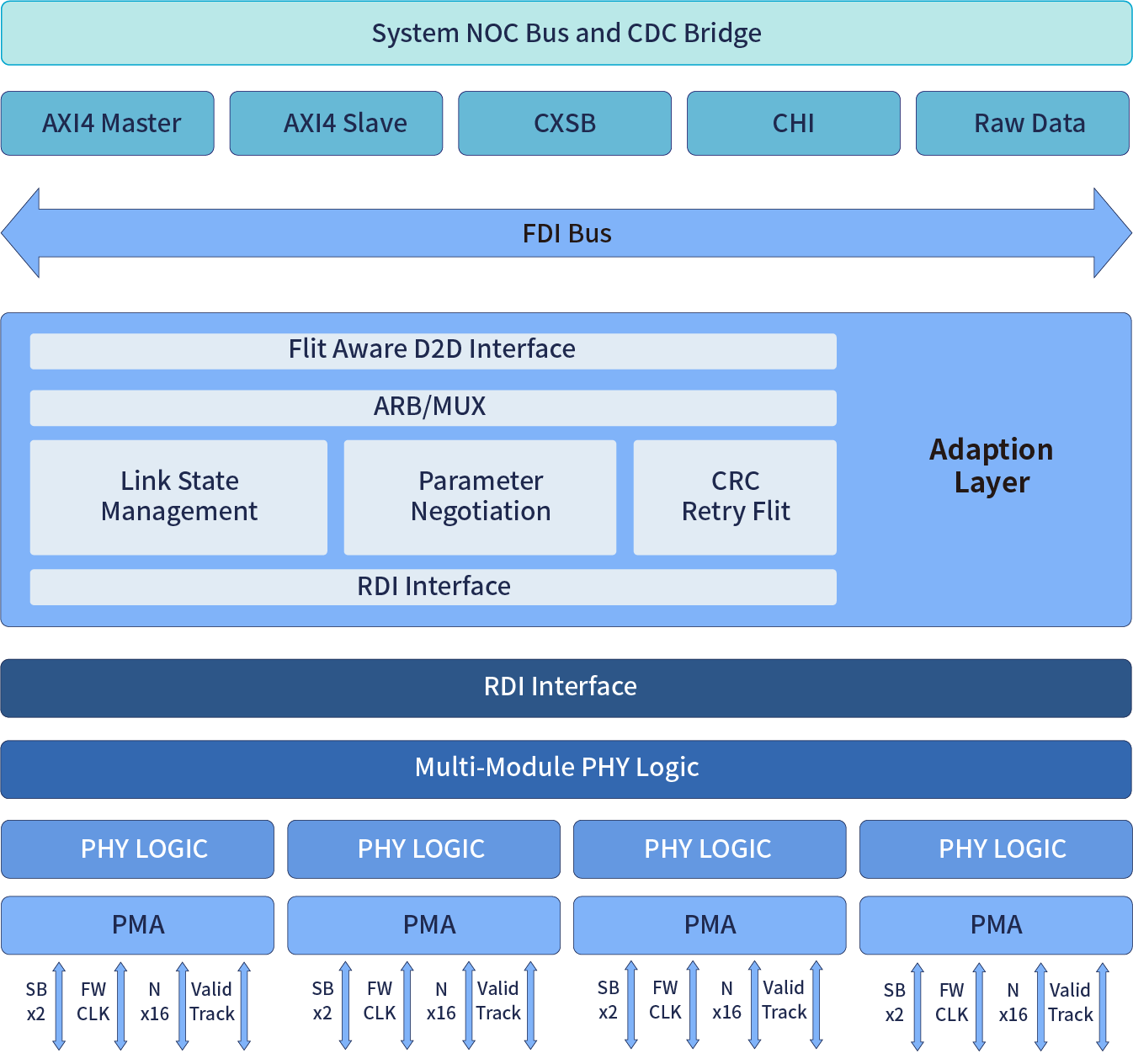

崇华明介绍,合见工软自主知识产权的全国产高速接口IP解决方案是合见工软更广泛的EDA+IP产品战略的重要组成部分,覆盖NPU、CPU、AI/GPU等主要智算芯片产品,支持多应用场景。在完整的PHY和控制器方案的助力下,能够有效解决安全和兼容性问题。 合见工软高速接口IP解决方案秉持“想客户所想,构建完整供应链生态”的理念,为客户提供整体的解决方案,协助客户设计低功耗、高性能并且具有高度差异化的芯片产品,缩短开发周期,提升良率,帮助客户提高竞争优势。 其中,合见工软的UCIe解决方案包括IP、子系统、封装和软件等,其优势和特色主要在于:

支持全栈协议的UCIe-SP、UCIe-AP。

UCIe端到端的解决方案:支持FDI、AXI、CXS.B等接口,具备多种协议层定制经验。

支持国内国外近10种工艺,速度最高可达32Gbps。

D2D标准封装模式,可以无缝支持C2C应用。

超低延迟、超低功耗的设计。

可扩展PCIe/CXL的协议层设计。

▲合见工软高速接口IP- UCIE解决方案

崇华明着重指出,合见工软的UCIe支持多场景互联,覆盖从标准封装到先进封装的全场景。标准封装中,支持Substrate(基板)、Interposer(硅中介层)、PCB(C2C)等形式。先进封装则支持 COWOS-S、COWOS-R等,能够满足客户的不同需求。此外,合见工软的UCIe还实现了多工艺流片保证兼容性,不同工艺UCIe均通过C2C互联兼容性测试,有助于客户高效打造Chiplet产品。

在标准演进与生态参与方面,合见工软作为UCIe 联盟成员及工作组贡献者,深度参与UCIe标准迭代工作。今年8月5日,UCIe联盟正式推出UCIe 3.0规范,进一步扩展速率范围最高达64Gbps,运行时重校准技术并完全向后兼容。崇华明表示,合见工软将会继续深耕UCIe IP,让更多的公司共享UCIe带来的益处。

同时,合见工软也积极关注并支持HiPi标准的快速演进。HiPi是我国主导的D2D标准,支持2D/2.5D封装,更加适合我国产业生态的D2D标准。

据崇华明介绍,HiPi标准与UCIe相比,有三方面优势。

首先,和UCIe相比,HiPi在信号BUMP的排布形态和顺序方面有所不同。优势在于,一方面在相同的带宽密度情况下,HiPi有机基板所需的层数是UCIe的一半。另一方面,通道内信号在同层走线,可以做到不同数据通道的时间延迟差非常小,减少电压温度漂移效应,可以支持更加恶劣的电路板和封装设计,可以支持系统设计达到更高的速度。

其次,HiPi时间延迟差的相位搜索功能在Rx上(UCIe在Tx),简化了Tx和Rx的交互,避免非常多的相容性问题,能够加快训练速度。

第三,HiPi数据通道之间的设计架构比较灵活,可以支持多种实现方式,实现更低的功耗。

崇华明强调,整体而言,HiPi与UCIe有相似之处,但也有很多创新,能够更好地匹配我国芯片产业的发展阶段和实际需求,是适应我国国情的互联标准。

在HiPi方面,合见工软推出了国内首个端到端HiPi IP/VIP整体解决方案。该方案支持HiPi标准封装;第一代产品支持到16Gbps;超低延迟的设计(PAIF2PAIF数据链路层延迟4ns)。

▲合见工软HiPi IP/VIP整体解决方案

在封装和仿真支持方面,合见工软高速接口IP的封装设计主要为2D和2.5D封装设计,支持20层Substrate;支持5层金属、厚铜和DTC的硅中介层以及RDL Interposer,同时还可以进行先进封装的SIPI和可生产性分析。基于合见工软提供的封装参考设计,合见工软高速接口HBM3E PHY,UCIe-AP PHY,UCIe-SPPHY等仿真和测试结果成效尤为明显。

总结而言,合见工软高速接口IP解决方案的优势在于:

一是完整的多工艺平台IP(UCIe、HBM、Ethernet/UEC-MAC、RDMA/PAXI 、PCIE5/32GMPS、LPDDR/DDR、HiPi),支持广泛颗粒和外设。

二是提供完整的PHY和控制器方案,解决安全和兼容性问题。

三是支持多场景应用,多种协议层定制经验支持客户产品快速落地。

四是深度参与HIPI-国内D2D的快速演进,推动国内标准和生态的建设。

五是提供封装设计,SIPI仿真支持,为芯片设计保驾护航。

演讲最后,崇华明表示,当前,UCIe IP正驱动Chiplet产品快速发展。合见工软作为国内唯一提供EDA工具+广泛IP的供应商,能够为客户提供自主可控的工具链,在服务广大智算芯片公司的同时,也将积极推动中国智算芯片产业的发展。