7月17-18日,在中国规模最大、规格最高的RISC-V峰会上,芯华章向数千名专业用户展示其面向RISC-V指令集打造的完整敏捷验证方案,其中最新发布的GalaxSim Turbo 3.0创新性地结合事件驱动和周期驱动双引擎在仿真性能上的优势,以自动负载调度算法提升并行仿真效率,在周期加速场景中,相比于传统商业仿真器相比可实现十倍以上的验证效率提升。

GalaxSim Turbo 3.0 双仿真引擎兼顾性能和易用性

随着现在设计复杂性的提高,传统的逻辑仿真器产品在很多场景下受限于事件的异步行为,设计的分割(Partition)和线程同步有较大的限制,往往无法支持高速的并行仿真,从而大大限制了验证的场景和规模。

GalaxSim Turbo高速仿真模式让用户在不需要修改验证环境的情况下,大幅提高了仿真并行度。同时混合仿真模式兼顾了传统仿真器对SystemVerilog语法和UVM特性的支持,结合XEDB波形合并、功能覆盖率分析等一系列实用的调试工具,有效确保了验证流程的连贯性。

使用门槛更低

支持Verilog/SystemVerilog全语法,额外支持SVA,Functional Coverage等Verilator没有的功能,同时可在原先的仿真用例上可以一键切换;

易用性更强不局限C Testbench,验证环境的移植平滑,维护成本大大降低;

并行效率高Verilator线程数目需要编译前指定,Turbo的线程数目可以在RunTime的时候根据服务器资源指定,大大提高多线程的管理效率;

仿真运行速度更快在拆分设计之前对设计描述方式和信号同步机制进行深度优化,同时可以根据客户设计特点进行特殊的定向优化;

运行资源管理优化运行时可以自动寻找合适的CPU资源,并得到计算资源,通讯资源的优化匹配;

调试能力强支持并行下载芯华章波形文件格式XEDB,波形文件大幅减小,下载速度显著提升,得到完整的一体化Debug体验。

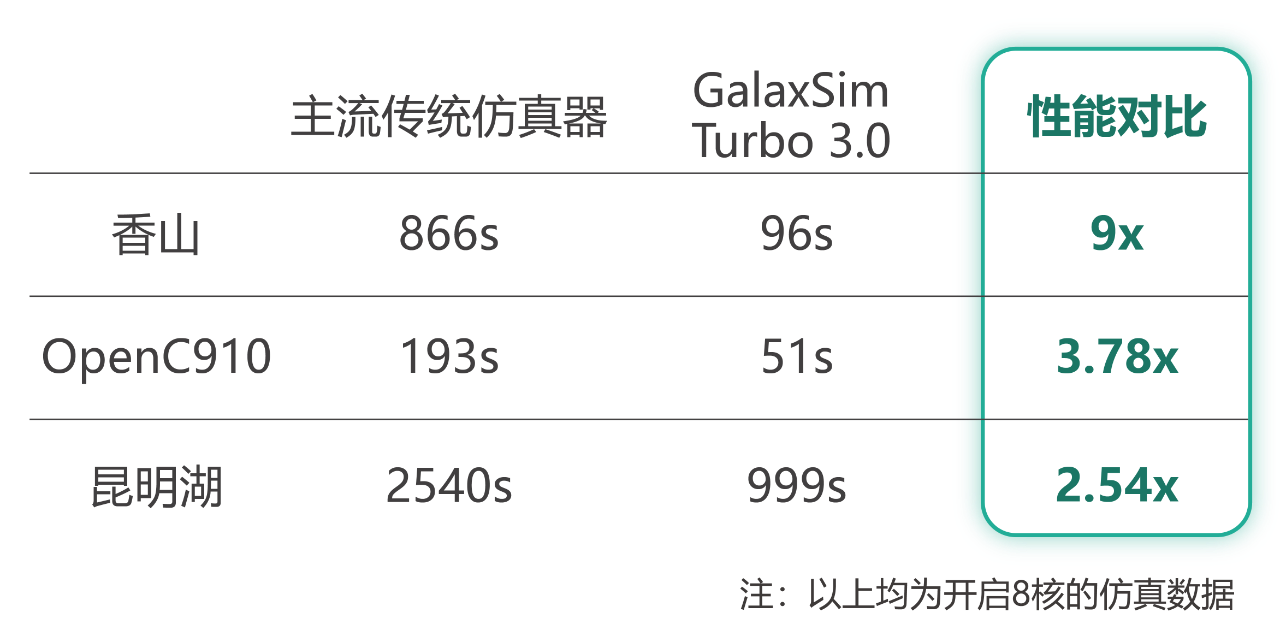

表1:RISC-V开源项目实践,验证效率显著提升

芯华章科技联席CEO谢仲辉表示:“在科技竞争异常激烈的今天,我们以AI赋能EDA技术革新的同时,也在积极地探索具有巨大潜能的应用场景,以更敏捷、更充分、更完备的验证方案,保障基于RISC-V架构相关产品的稳定性,从而助力RISC-V其获得大规模的商业部署,发展中国自主可控的RISC-V架构芯片服务于市场。”

芯华章在与芯来、开芯院、国家集成电路设计自动化技术创新中心、中国科学院计算技术研究所等多家客户深度合作中,产品也在不断升级,帮助客户解决从IP高度定制化到系统软硬件协同验证等一系列挑战。

RISC-V 具有高度可定制化和场景复杂的特点,在AI芯片定制当中,设计者为了提高计算效率、支持如浮点运算、AI算子等特定应用需求,往往会对传统处理器指令(如RISC-V)进行扩展定制,而其计算复杂度高,验证难度大,使用传统验证方法难以做到有效完备验证。

GalaxEC

面向EDA 2.0目标,芯华章运用新一代形式化求解算法和并行计算技术打造高性能求解引擎,GalaxEC基于形式化底层技术,能一站式满足用户全流程等价性验证需求,避免多工具切换成本,帮助工程师确保不同层次设计之间的一致性,同时,GalaxEC HEC可完备验证RISC-V处理器算子实现的正确性,包括算术逻辑单元ALU、整数运算单元及浮点运算单元等C++算法模型到RTL实现的等价性,可支持原生云部署,更好地满足敏捷验证与设计需要。

基于RISC-V的应用系统需要系统级验证及软件适配,更多软件生态需要移植到RISC-V处理器,但由此带来的bug是软件问题还是硬件问题?定位和调试困难,需要更强大的软件代码-硬件电路联合调试手段。

HuaPro P3

HuaPro P3采用最新一代可编程SoC芯片,结合自研的HPE Compiler工具链 ,可支持容量更大、速度更快、更多最新高速接口的用户芯片设计;同时,对基于RISC-V等多种异构处理器架构的定制化高性能应用芯片,HuaPro P3的软硬件系统可支持自动化和智能化的实现流程、支持灵活模块化扩展和云部署,有效减少用户人工投入、缩短芯片验证周期,兼顾验证性能和深度调试的需求。

关于第五届RISC-V中国峰会

RISC-V中国峰会是全球三大RISC-V专业会展之一,也是中国规模最大的RISC-V年度活动。

本届由上海开放处理器产业创新中心(SOPIC)主办,旨在协同RISC-V产业链上下游企业,共建RISC-V关键共性技术平台,用开放的硬件平台构建开源的软件生态,从而有力促进RISC-V技术的产业化应用和商业化落地。

来源:芯华章科技