硅芯科技自研3Sheng Integration Platform,实现三维堆叠芯片的系统级规划、物理实现与分析、可测性与可靠性设计等,集成“系统-测试-综合-仿真-验证”五引擎合一,具有统一数据底座,支持三维异构集成系统的敏捷开发与可定制化的协同设计优化,并在多个功能和性能上具有独创性。

引言

三维集成电路(3D IC)已为后摩路径中的产品设计提供了极大的灵活、便利与复用性,越来越多的AI算力与高端数模混合集成正在运用堆叠芯片架构来获得下一代产品。堆叠芯片与先进封装技术对产品的性能、功能、成本、迭代方式均至关重要。

然而,三维堆叠芯片(2.5D/3D/3.5D)包含多个堆叠芯片(Stacked Die),这些Die通过中介层上特殊过孔(via)或互连凸块(bump)来实现所需的连接。然而,根据工艺规则独立验证这些独立Die和基板的物理集成与之互连精度,并不能确保整个2.5D/3D封装系统得到最终的正确,设计者们需要针对多种堆叠方式进行自动化的验证,包括版图原理图一致性与设计规则。

3Sheng Stratify™(EDA)工具为堆叠芯片设计中的Die与Die之间、Die与中介层互连接口提供快速、准确的组装级验证。对于来自多个工艺节点的Die设计的互连进行操作,从物理规则与设计版图层面完成堆叠芯片的版图和原理图(LVS)一致性验证与设计规则检查(DRC)。

硅芯3DIC紫皮书展示了现版本3Sheng EDA中堆叠芯片的物理验证——从2D到3D集成的自动化方法,从基本的堆叠结构版图原理图对比检查、异常互连问题、堆叠连接完整性检查获得版图的验证;从2D到3D集成的设计规则和违例分析与自动校正,获得设计规则的查验,最终确保物理设计的准确性和堆叠系统性能上的完整。

01 工具应用场景

1.1 设计需求

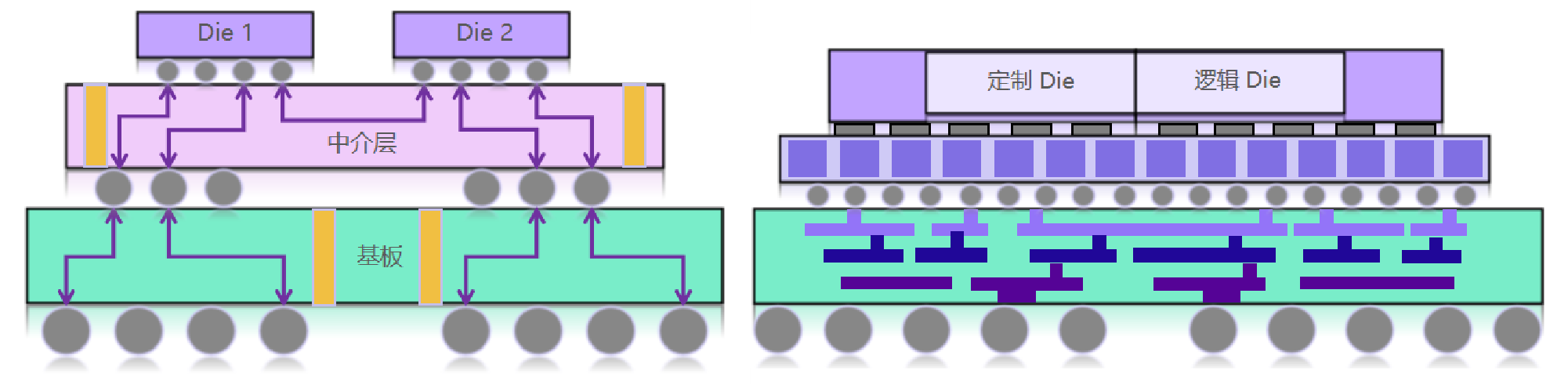

高互连密度先进封装在各种终端应用中出现持续增长的势头。一方面,使用中介层(硅/有机)的2.5D堆叠芯片集成系统通常针对军事、航空航天和高端算力需求的产品应用;另一方面,而3D扇出封装方法更侧重于手机等大众消费类应用。不仅如此,所有主流的的芯片设计公司、代工厂和封装测试(OSAT)公司都不断积极布局基于三维集成的后摩技术路径,包括2.5D和使用硅通孔(TSV)或混合键合的3D堆叠。

图1 高互连密度先进封装类型 (2.5D/3D/3.5D/SiP/FOWLP/MCM)

而堆叠芯片设计的验证的电子设计自动化(EDA)涉及多个方面的理验证解决方案,包括不限于:

◆ 先进封装的组装级的版图和原理图一致性验证

◆ 高密度互连系统级生成式,跨Die和封装接口的寄生效应的验证

◆ 用于先进封装的版图后模拟的仿真和数字的静态时序分析(STA)

◆ 对于封装设计配备的工艺套件(ADK)的开发

◆ 解决3DIC验证中数据完整性的签核验证

根据自动化设计需求,硅芯科技总结了设计者们对验证的三大基本需求:

1. 连接性:通过封装-中介层布线验证多个Die是否正确的连接验证。

2. 互连对准:验证多个Die是否按预期在封装-中介层顶部对齐验证互连的垂直对齐。

3. 跨Die/跨层设计规则检查:验证复杂互连结构中的信号线避免互相影响导致的信号和功能完整性的检查。

1.2 SiChip物理验证工具方案

工具功能概览

3Sheng Stratify™(EDA)工具为堆叠芯片设计中的Die与Die之间、Die与中介层互连接口的电气验证,完成来自多个工艺节点的Die设计的互连进行操作:

◆ DRC:在设计规则中,从2D的基本设计规则到跨Die的多种新型影响先进封装工艺的规则完成检查。

◆ LVS:从堆叠芯片结构的原理图和版图对比中完成一致性检查。

关键性能指标

◆ 跨层级一致性验证

◆ 网表与物理布局联动分析

◆ 异常网络智能自动化检测

◆ 多文件协同检查

◆ 2.5D连接规则校验

◆ 自定义互连规则配置

◆ 覆盖关键DRC规则,多层间检查

◆ 特殊工艺检查、符合Foundry规范

◆ 高效的多层DRC分析

◆ 针对2.5D跨层连接,避免SI/PI问题

◆ 高效计算引擎,提升大规模GDS迭代效率

◆ 支持部分违例自修复,修正潜在工艺问题

02 版图原理图一致性检查

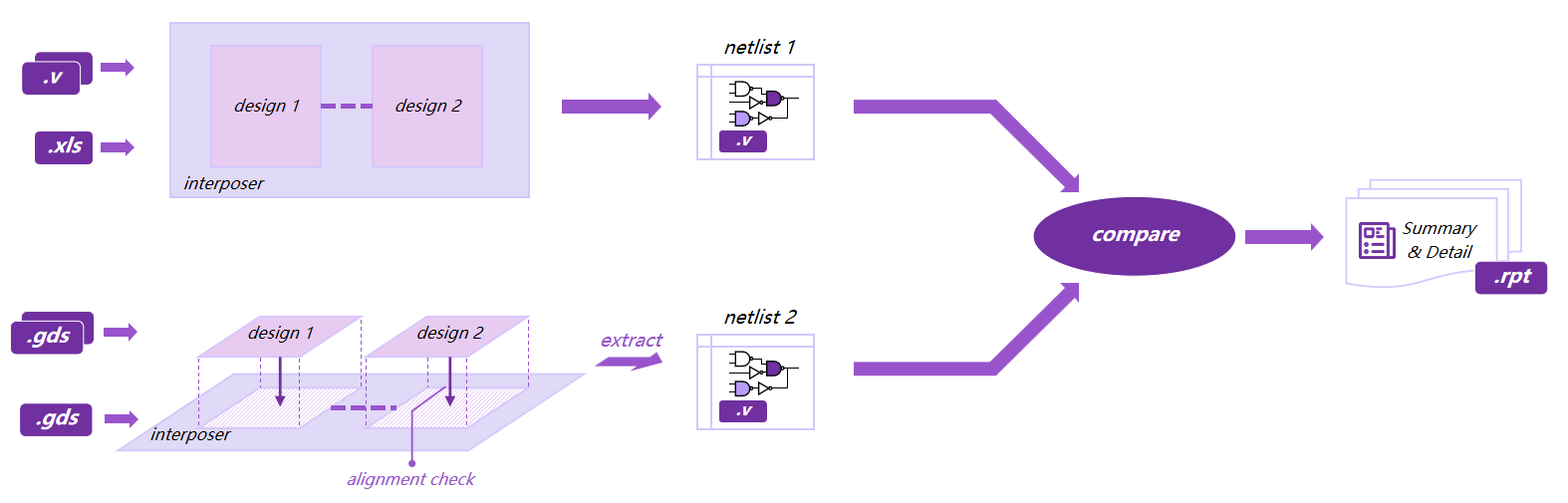

在复杂3DIC设计中,确保多个Chiplet间的正确连接至关重要。3Sheng_LVS通过解析Verilog代码、GDS层之间的连接关系完成全面的连通性检查。这种方法有效地验证了Chiplet间物理连接,提高设计效率,缩短多芯片集成设计周期。

2.1 LVS版图原理图一致性检查

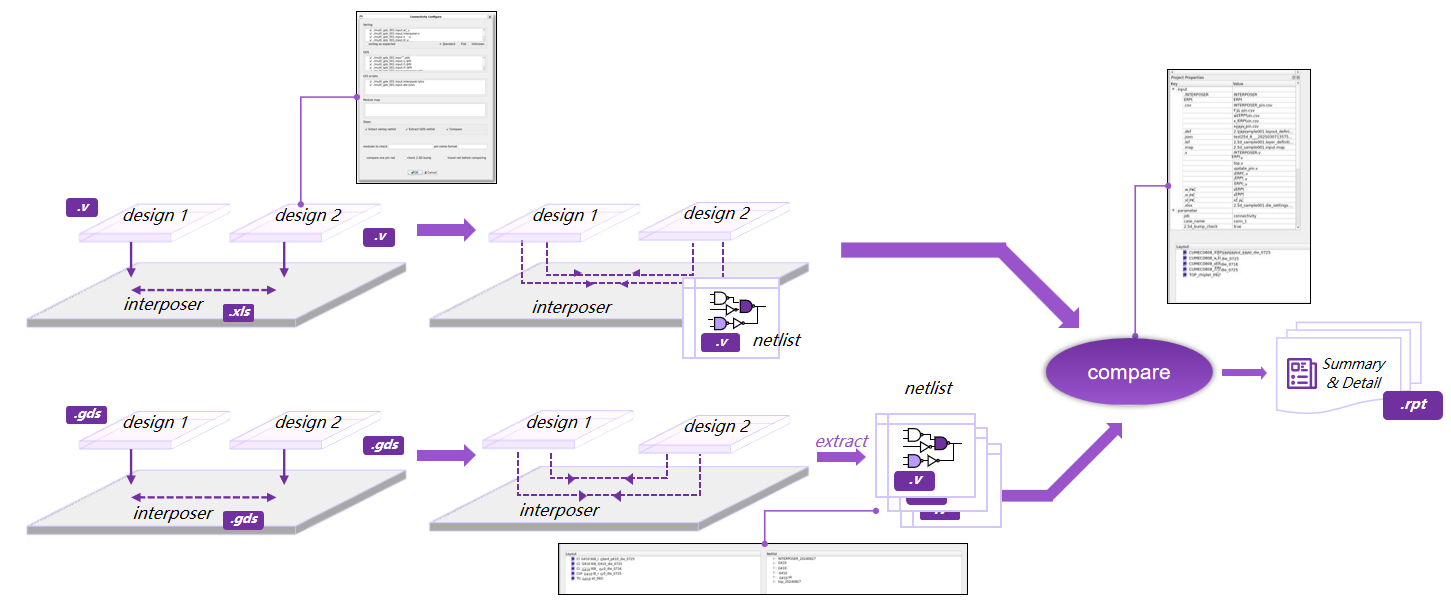

在2.5D布线完成后,需要对硅中介层与各Chiplet之间的连接性进行细致检查,确保GDS与网表的一致性。其中包括网表与物理布局的联动分析,以支持最终需要完成的系统级异构集成。

图2 3Sheng 2.5D LVS验证流程

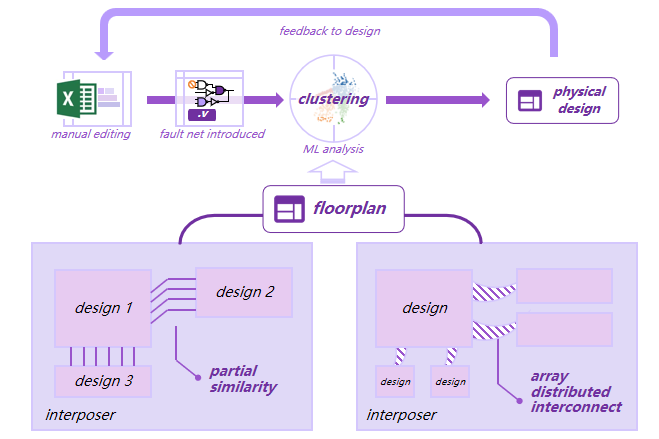

2.2 2.5D异常设计检查(ADC)

LVS检查基于原理图和最终版图的一致性对比,2.5D布线的跨Die连接在局部区域的连接上,具有长度、相对位置、方向等物理特性的相似性。而由设计中引入的错误编辑(不论是人工或工具)的网络连接在这些物理特性上具有特异性。

若2.5D设计多采用excel等文本编辑方式进行,并且2.5D的网络规模庞大,所同构die的阵列重复性高,仍然会引入错误设计,如网络会被错误地连接到同构的不同实例上去。

3Sheng LVS工具在功能上,基于2.5D设计的局部性和同构阵列的网络连线特点,在基于网表和版图的连线关系的解析中,运用机器学习算法(聚类)进行异常设计检查,可准确地推测出异常网络的位置,进而反馈设计。

图3 3Sheng 2.5D异常设计检查

2.3 2.5D连接规则校验

在传统的2D芯片中,对连接关系通常为一一对应检查,而在2.5D集成中,LVS不仅需要支持单芯片的verilog检查,更要支持多对多的系统性检查。包括:

◆芯片内部的连通性检查

◆ 芯片到中介层的连通性的检查

◆ 中介层到BGA和封装基板的连接检查

工具为提高了各层级、各引脚和连接关系检查的扩展性,支持跨多个Verilog和多个GDS文件的电路连接检查,自上而下地完成复杂的多芯片设计。

图4 3Sheng 2.5D完整连通性检查

03 2.5D设计规则检查

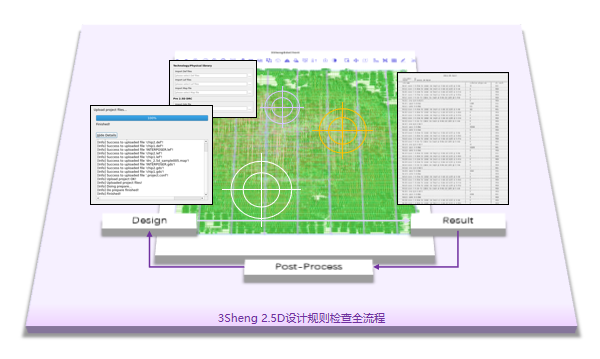

3Sheng_Veri 2.5D设计规则检查工具结合先进的DRC算法,通过解析GDS数据,对多Chiplet之间的布线、间距、过孔连接等关键设计规则进行全面检查,可以有效验证 2.5D 设计中不同Chiplet及Interposer之间的物理布局是否满足制造工艺规范,从而提升设计的可制造性和可靠性。

图5 3Sheng 2.5D设计规则检查流程

3.1 主流DRC规则检查

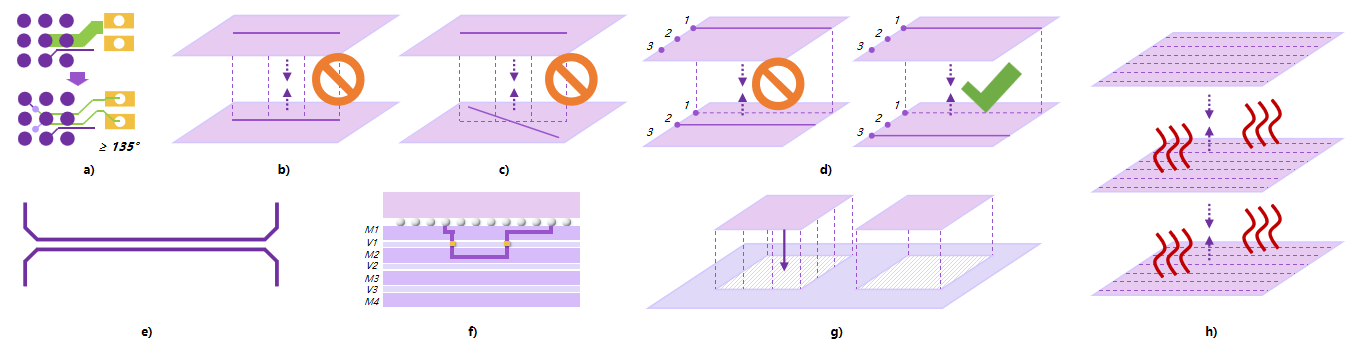

3Sheng DRC工具支持丰富的DRC检查,包括常规的几何规则、多层间检查,特殊工艺检查、符合Foundry规范,以及支持自定义规则。包括不限以下:

工具功能概览

◆ 识别和支持布线角度检查

◆ 在对不同metal之间via连通性的检查

图6 3Sheng 2D设计规则检查

2D设计规则检查

◆ 对Die和interposer的高密度互连覆盖度检查。

◆ 完成差分线等长、等距的检查。

◆ 支持识别多种Die内不同层高速信号线的串扰隐患,包括导线重叠、映射交叉、间距不足等情况。

图7 3Sheng 2.5D设计规则检查

3.2 DRC分析与校正

3Sheng DRC工具支持丰富的DRC检查、自动修复和高速计算引擎。支持Die内跨层间距、重叠检查、高速信号线间距、差分线、Shielding等检查,并针对2.5D的跨层连接,支持避免SI/PI问题,包括不限以下:

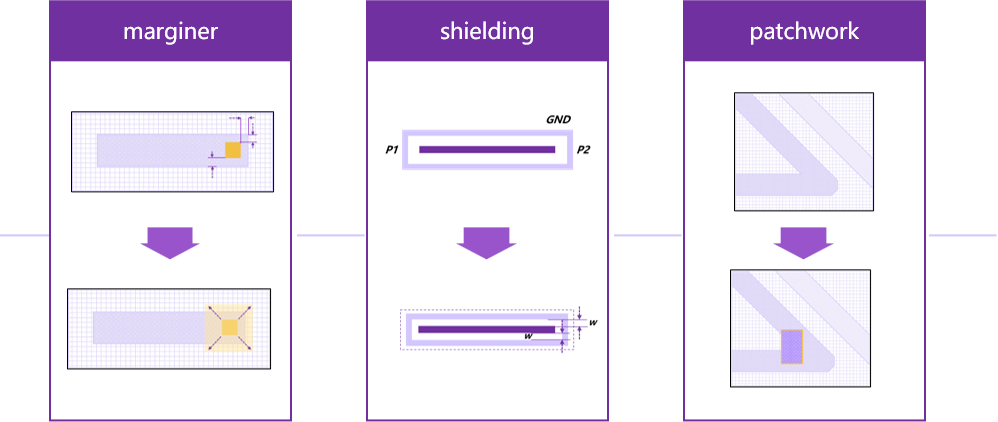

◆ Marginer:工具执行APR时,线端的内部孔边间隔,可能因为过小而出发工艺违规,通过3Sheng DRC边缘检查功能实现自动化修复,可以减少人工操作,加快迭代。

◆ Shielding:差分线负责关键信号,其特定的规则表现在内部间隔(inner-spacing),正常的间隔约等于线宽,以达到最佳的屏蔽效果。3Sheng DRC的扩展规则的检查,支持间隔与线宽关系的识别,以帮助完成有效设计。

◆ Patchwork:当金属线之间存在非常小的角度,就会发生工艺规则违规。该情况下,工具可以识别其违规,并进行自动补丁(patchwork),达到减少因小角度产生的工艺失效问题。

图8 3Sheng 2.5D设计规则违例自动修复

物理设计工具3Sheng Stratify™是支持多芯片堆叠组装的检查工具,可以快速轻松地验证物理多芯片的实现准确性、互连完整性以及相关的电性能,可以帮助企图快速完成堆叠芯片系统的设计者们进行快速签核,检查与校正设计的物理属性,消除不必要的调试迭代,加速产品上市。

同时,3Sheng Integration Platform是“架构-测试设计-物理设计-协同仿真-验证”五引擎合一的Chiplet快速设计工具:

● 通过架构设计和早期分析完成堆叠版图规划与预设计

● 通过在互连设施中的早期的测试容错设计完成堆叠芯片系统的可测性和容错修复配置

● 通过物理实现完成大规模、高互连密度结构的电热感知和布线优化的快速收敛

● 通过协同设计仿真,完成系统的设计指标,确保封装设计、性能、功耗、面积与成本设计的权衡

● 通过LVS/DRC物理验证完成系统的签核

● 通过兼容其他工具,完成可靠性设计

硅芯科技持续致力于2.5D/3D/3.5D/晶上集成系统的多场景自动化设计功能的完善与扩展,希望为业内提供更完整和便捷的设计与验证方案,协同先进封装方案,打造STCO的完整模式。

关于硅芯

珠海硅芯科技有限公司主要从事新一代2.5D/3D堆叠芯片EDA软件设计的研发及产业化。三维集成电路(堆叠芯片)设计EDA是具有重要意义的技术创新产品,通过堆叠芯片设计实现更高性能、更高集成度、更高可靠性和更低功耗的芯片系统,不仅能够填补国产芯片EDA软件的差距,同时借助2.5D/3D堆叠芯片的行业趋势,助力国产芯片设计行业产业升级,推动RISC-V, AI, GPU, CPU, NPU等各类芯片及终端应用领域发展。

来源:硅芯科技