4月24日,台积电在美国召开“2025年北美技术研讨会”,在本次北美技术研讨会上,台积电展示了其在先进制程、封装技术、特殊工艺以及面向新兴应用领域的多项技术突破和规划。以下是此次研讨会中提到的主要技术内容:

1. 先进制程技术

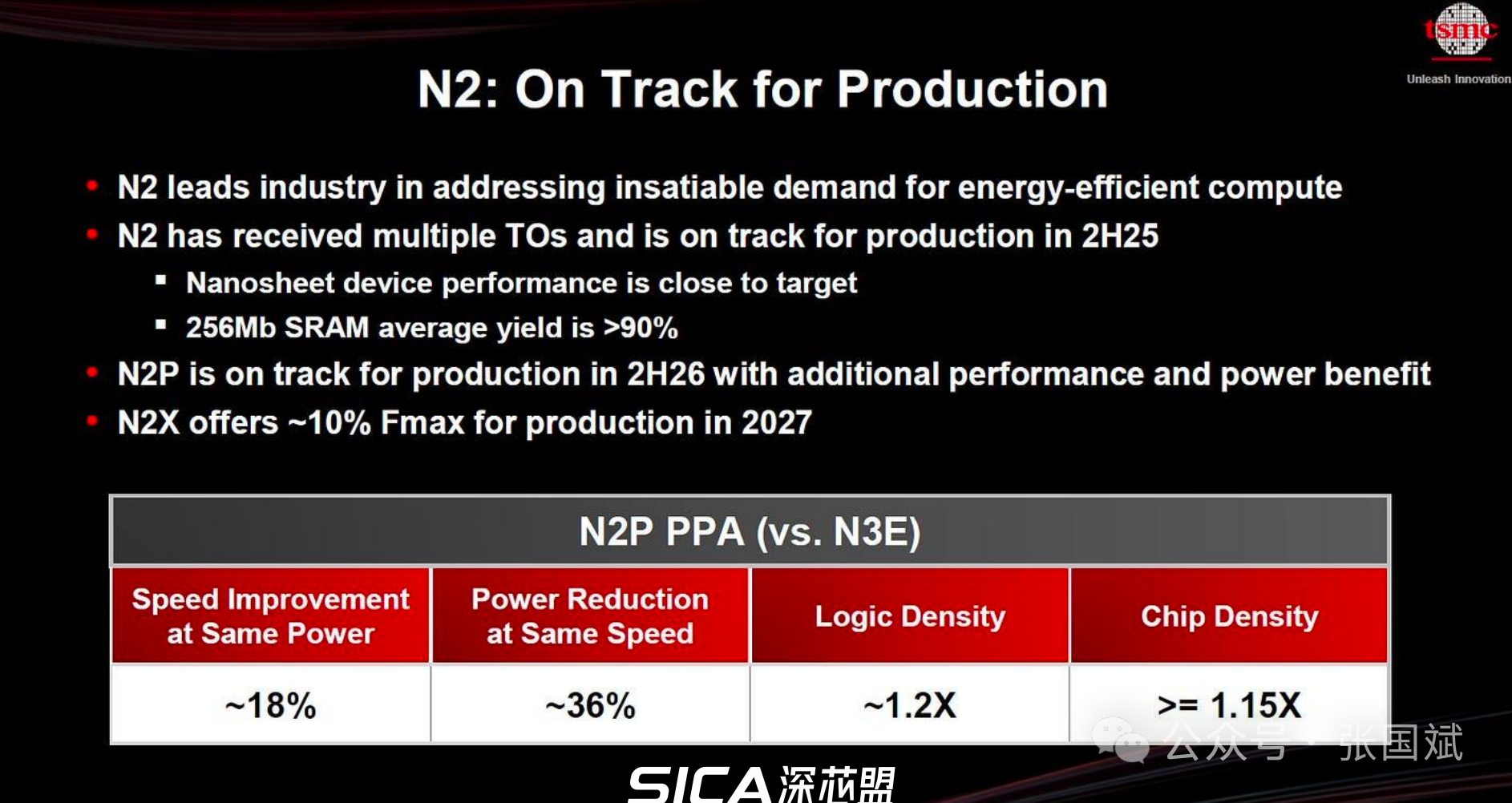

N2制程(2纳米):预计于2025年下半年量产,采用纳米片晶体管技术,性能较N3E提升18%,功耗降低36%,逻辑密度增加1.2倍。N2工艺节点的客户采用速度远超前代产品。

A16制程(2纳米级):计划于2026年下半年量产,融合了NanoFlex晶体管架构、超级电轨(SPR)技术和设计技术协同优化(DTCO)。SPR技术实现了背面供电网络,减少了布线拥塞和电源噪声。

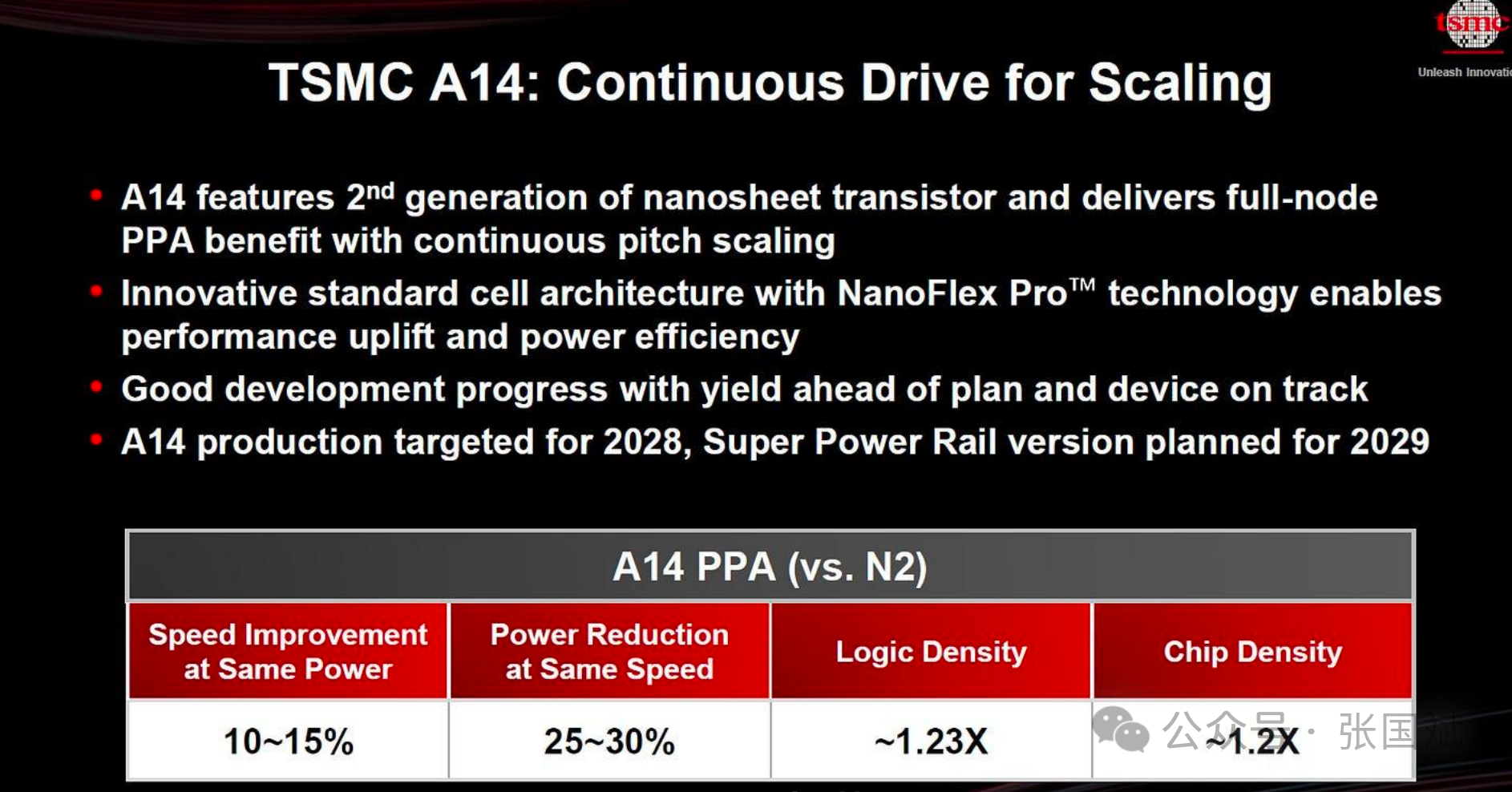

A14制程(1.4纳米):预计2028年量产,速度较N2提升15%,功耗降低30%,逻辑密度增加20%以上。A14制程未配备超级电轨技术,但计划在2029年推出A14 SPR版本。

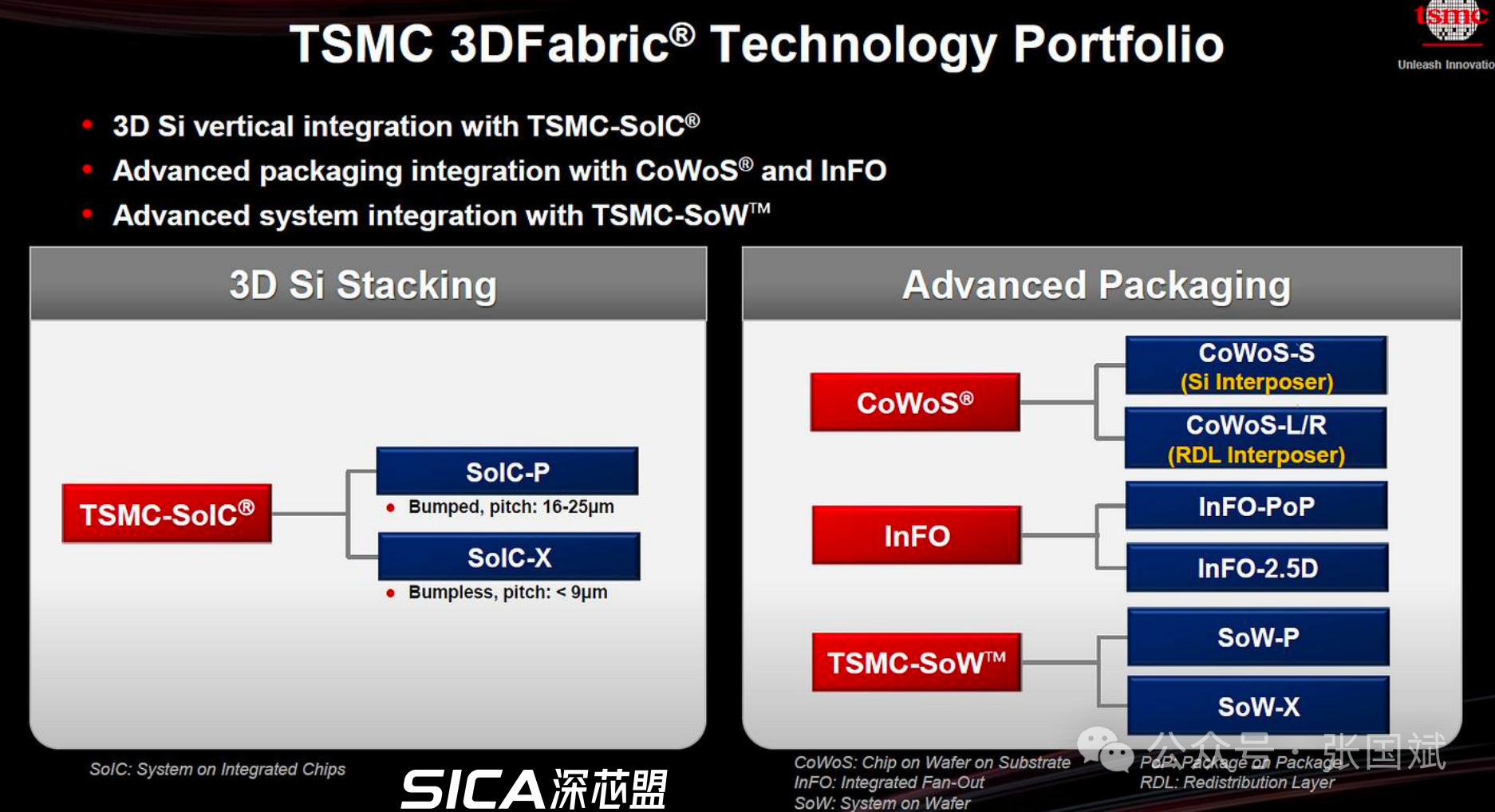

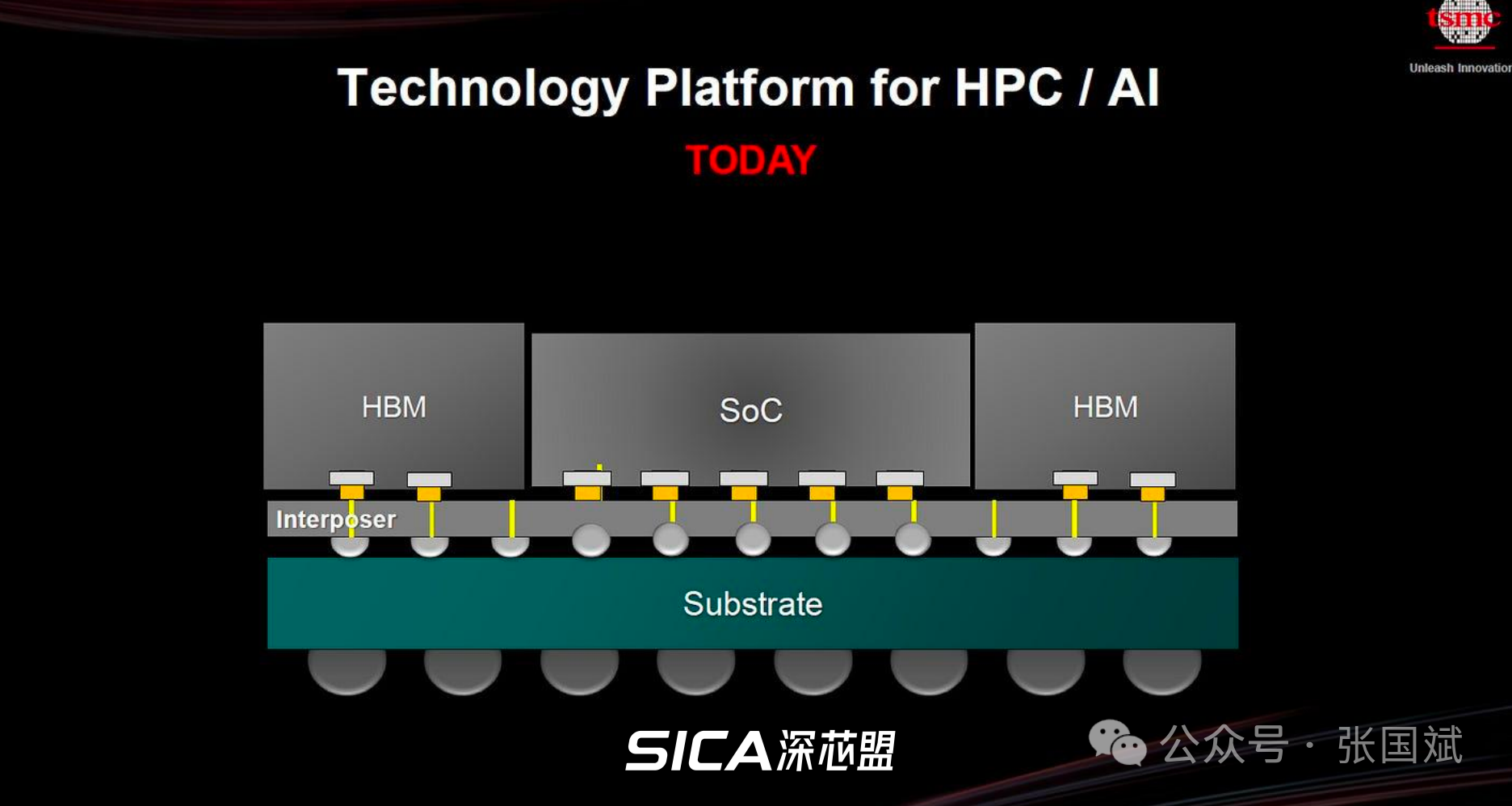

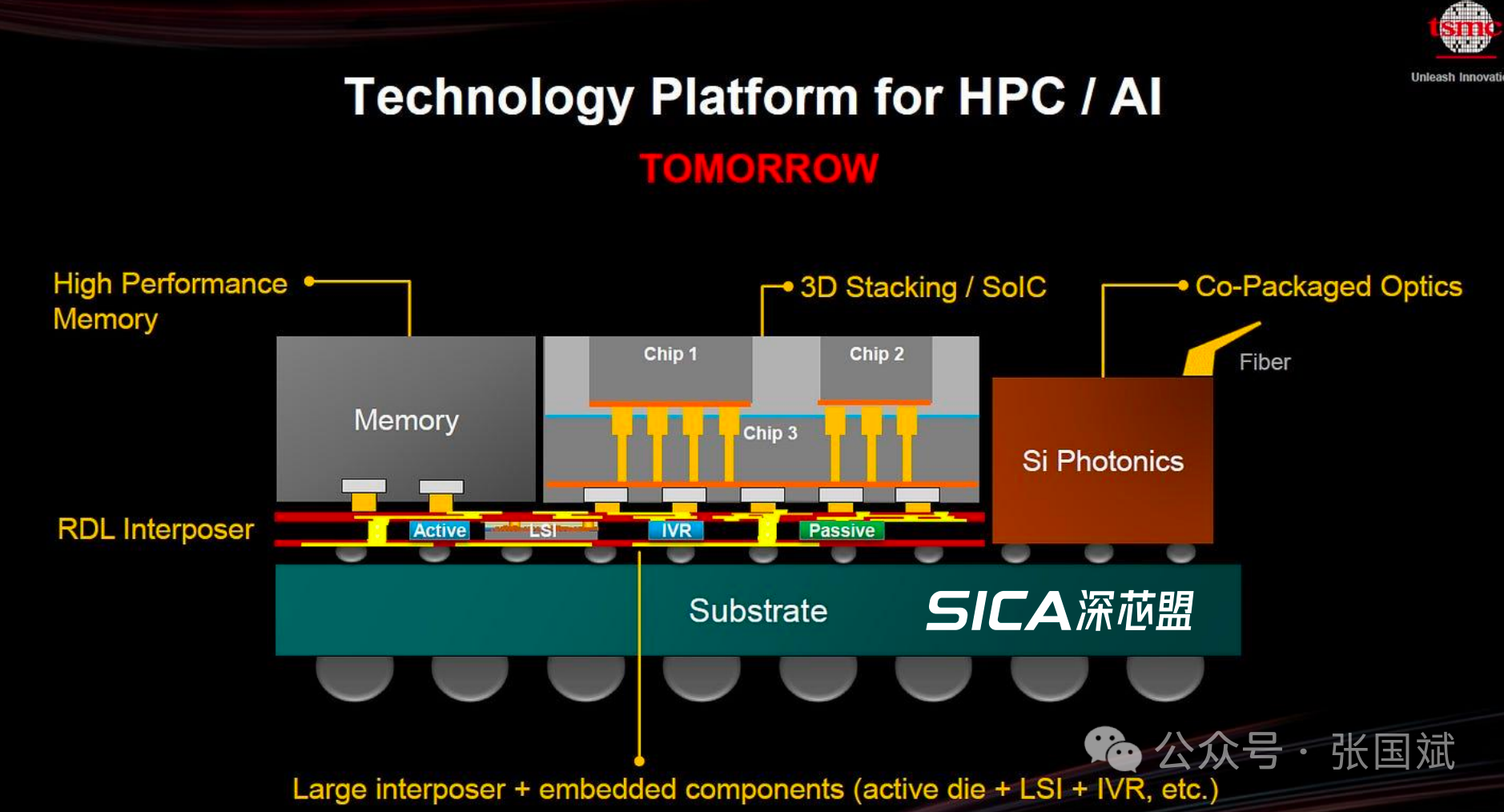

2. 封装技术

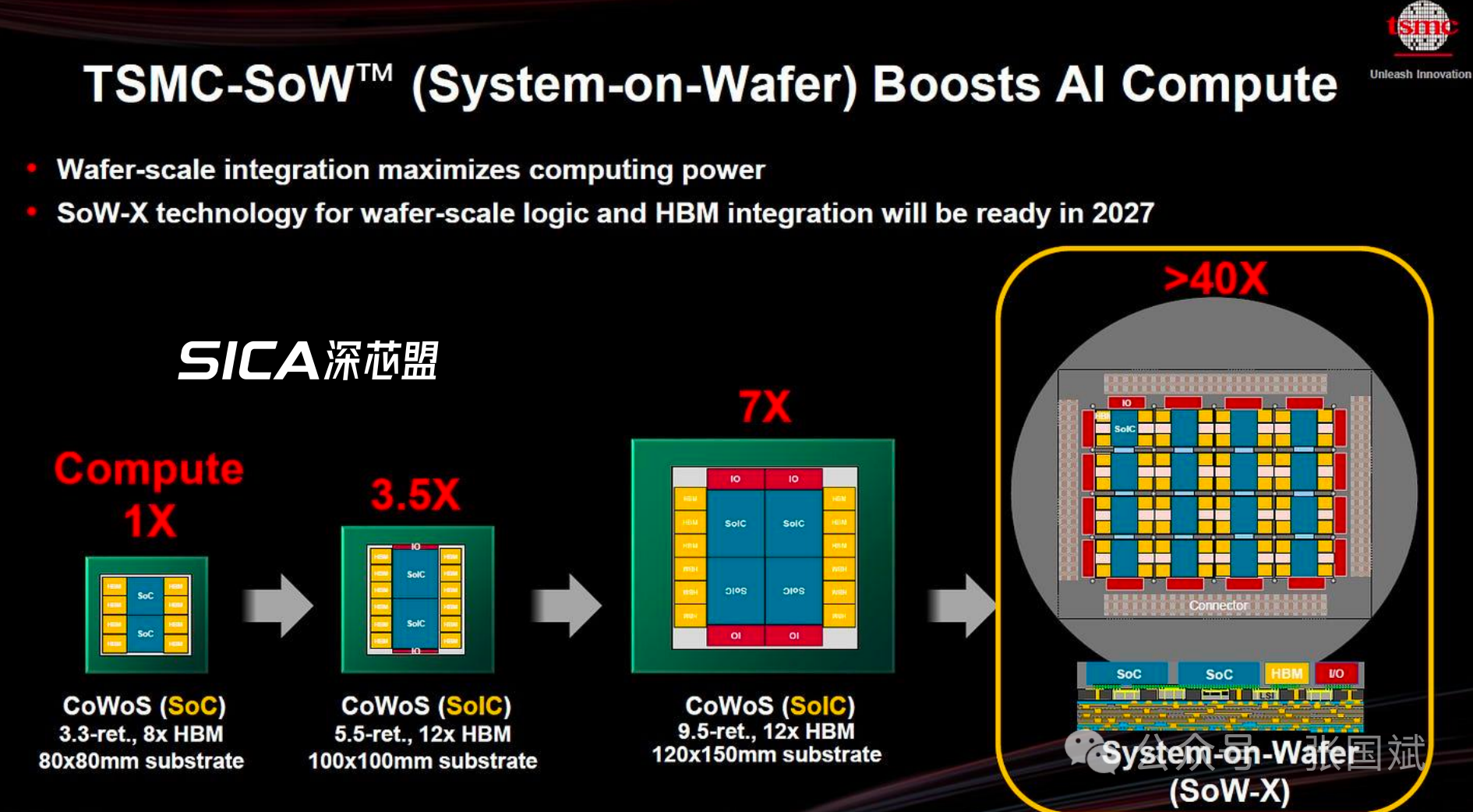

3DFabric先进封装技术:包括CoWoS、SoIC、InFO和SoW等技术。CoWoS技术继续推进,计划在2027年量产9.5倍光罩尺寸的CoWoS,能够将12个或更多的HBM堆叠整合到一个封装中。

SoW-X:基于CoWoS技术,计划于2027年量产,将提供40倍于当前CoWoS解决方案的运算能力。

SoIC技术:2025年量产,以6微米间距实现N3与N4芯片的垂直互联,2029年计划完成A14与N2的跨节点堆叠。

3. 特殊工艺与技术

高数值孔径极紫外光(High-NA EUV)光刻技术:A14制程可能会导入该技术,进一步缩小图案尺寸。

硅光子整合:运用紧凑型通用光子引擎(COUPETM)技术,用于高性能计算(HPC)和AI应用。

新型整合型电压调节器(IVR):用于AI芯片,具备5倍的垂直功率密度传输。

N4C RF射频平台:降低30%功耗与面积,支持WiFi 8等AI无线标准。

N3A工艺:通过汽车级认证,服务高级驾驶辅助系统(ADAS)与自动驾驶(AV)。

N4e工艺:针对超低功耗物联网AI设备。

4. 新兴应用领域的技术赋能

高性能计算(HPC):通过先进制程和封装技术,满足AI对更多逻辑和高频宽内存(HBM)的需求。

增强现实(AR):通过先进制程压缩显示引擎体积、优化低延迟通信芯片、开发高能效PMIC。

人形机器人:提供高性能AP、高精度MCU、CIS与LiDAR等芯片,支撑系统长效运行。

5. 其他技术与战略

全球产能布局:台积电通过全球化产能布局(如在美国、日本、欧洲的新厂)应对地缘政治与供应链风险。

绿色制造:台积电展示了其在绿色制造方面的成就,强调可持续发展。

Open Innovation Platform®生态系统:通过开放创新平台加速设计时间,提升客户的技术落地速度。

本文以图片形式分享台积电业务发展高级副总裁张晓强(KevinZhang)博士的PPT

台积电继续推进其晶圆上芯片 (CoWoS®) 技术,以满足人工智能对更多逻辑和高带宽内存 (HBM) 的无限需求。公司计划在 2027 年实现 9.5 微粒尺寸 CoWoS 的量产,从而在一个封装中集成 12 个或更多 HBM 堆栈,并采用台积电的尖端逻辑技术。在 2024 年展示了革命性的片上系统(TSMC-SoW™)技术后,台积电又推出了 SoW-X,这是一款基于 CoWoS 的产品,可创建计算能力是当前 CoWoS 解决方案 40 倍的晶圆级系统。计划于 2027 年实现量产。

同时在本次研讨会上,台积电还发布了下一代尖端逻辑制程技术 A14。A14 是台积公司业界领先的 N2 工艺的重大进步,旨在通过提供更快的计算速度和更高的能效推动人工智能转型。预计它还将通过提高智能手机的板载人工智能功能,使其更加智能。A14 计划于 2028 年投入生产,目前的研发工作进展顺利,良品率也比计划提前。

与即将于今年晚些时候投入量产的 N2 工艺相比,A14 将在相同功耗的情况下提高 15%的速度,或在相同速度的情况下降低 30% 的功耗,同时提高 20% 以上的逻辑密度。凭借公司在纳米片晶体管设计-技术协同优化方面的经验,台积公司还将其台积电 NanoFlex™ 标准单元架构发展为 NanoFlex™ Pro,从而实现更高的性能、能效和设计灵活性。