与泛林一同探索先进节点上线边缘粗糙度控制的重要性

作者:

Coventor(泛林集团旗下公司)半导体工艺与整合团队成员Yu De Chen

原文链接:

介绍

由后段制程(BEOL)金属线寄生电阻电容(RC)造成的延迟已成为限制先进节点芯片性能的主要因素[1]。减小金属线间距需要更窄的线关键尺寸(CD)和线间隔,这会导致更高的金属线电阻和线间电容。图1对此进行了示意,模拟了不同后段制程金属的线电阻和线关键尺寸之间的关系。即使没有线边缘粗糙度(LER),该图也显示电阻会随着线宽缩小呈指数级增长[2]。为缓解此问题,需要在更小的节点上对金属线关键尺寸进行优化并选择合适的金属材料。

除此之外,线边缘粗糙度也是影响电子表面散射和金属线电阻率的重要因素。图1(b)是典逻辑5nm后段制程M2线的扫描电镜照片,可以看到明显的边缘粗糙度。最近,我们使用虚拟工艺建模,通过改变粗糙度振幅(RMS)、相关长度、所用材料和金属线关键尺寸,研究了线边缘粗糙度对线电阻的影响。

图1:(a) 线电阻与线关键尺寸的关系;(b) 5nm M2的扫描电镜俯视图(图片来源:TechInsights)

实验设计与执行

在晶圆厂里,通过改变线关键尺寸和金属来进行线边缘粗糙度变化实验很困难,也需要花费很多时间和金钱。由于光刻和刻蚀工艺的变化和限制,在硅晶圆上控制线边缘粗糙度也很困难。因此,虚拟制造也许是一个更直接和有效的方法,因为它可以“虚拟地”生成具有特定线边缘粗糙度的金属线结构,进而计算出相应显粗糙度条件下金属的电阻率。

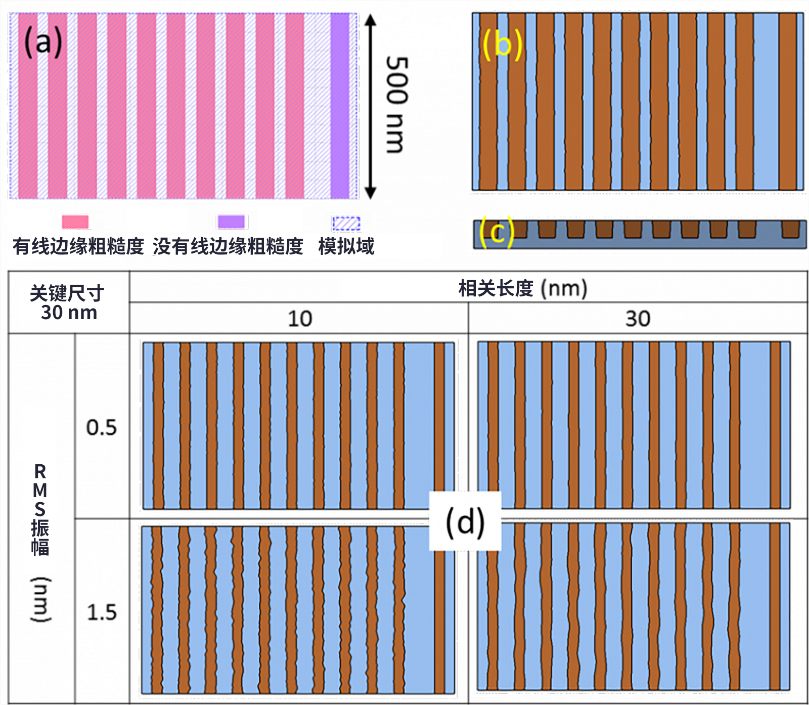

图2(a)显示了使用虚拟半导体建模平台 (SEMulator3D®) 模拟金属线边缘粗糙度的版图设计。图2(b)和2(c)显示了最终的虚拟制造结构及其模拟线边缘粗糙度的俯视图和横截面图。通过设置具体的粗糙度振幅(RMS)和相关长度(噪声频率)值,可以在虚拟制造的光刻步骤中直接修改线边缘粗糙度。图2(d)显示了不同线边缘粗糙度条件的简单实验。图中不同RMS振幅和相关长度设置条件下,金属的线边缘展示出了不同的粗糙度。这些数据由SEMulator3D的虚拟实验仿真生成。为了系统地研究不同的关键尺寸和材料及线边缘粗糙度对金属线电阻的影响,使用了表1所示的实验条件进行结构建模,然后从相应结构中提取相应条件下的金属线电阻。需要说明的是,为了使实验更为简单,模拟这些结构时没有将内衬材料纳入考虑。

图2:(a) 版图设计;(b) 生成的典型金属线俯视图;(c) 金属线的横截面图;(d) 不同RMS和相关长度下的线边缘粗糙度状态

表1: 实验设计分割条件

实验设计结果与分析

为了探究线边缘粗糙度对金属线电阻的影响,用表1所示条件完成了约1000次虚拟实验设计。从这些实验中,我们了解到:

1.当相关长度较小且存在高频噪声时,电阻受到线边缘粗糙度的影响较大。

2.线关键尺寸较小时,电阻受线边缘粗糙度RMS振幅和相关长度的影响。

3.在所有线关键尺寸和线边缘粗糙度条件下,应选择特定的金属来获得最低的绝对电阻值。

结论

由于线边缘粗糙度对较小金属线关键尺寸下的电阻有较大影响,线边缘粗糙度控制在先进节点将变得越来越重要。在工艺建模分割实验中,我们通过改变金属线关键尺寸和金属线材料研究了线边缘粗糙度对金属线电阻的影响。

在EUV(极紫外)光刻中,由于大多数EUV设备测试成本高且能量密度低,关键尺寸均匀性和线边缘粗糙度可能会比较麻烦。在这种情况下,可能需要对光刻显影进行改进,以尽量降低线边缘粗糙度。这些修改可以进行虚拟测试,以降低显影成本。新的EUV光刻胶方法(例如泛林集团的干膜光刻胶技术)也可能有助于在较低的EUV曝光量下降低线边缘粗糙度。

在先进节点上,需要合适的金属线材料选择、关键尺寸优化和光刻胶显影改进来减小线边缘粗糙度,进而减少由于电子表面散射引起的线电阻升高。未来的节点上可能还需要额外的线边缘粗糙度改进工艺(光刻后)来减少线边缘粗糙度引起的电阻。

参考资料

[1] Chen, H. C., Fan, S. C., Lin, J. H., Cheng, Y. L., Jeng, S. P., & Wu, C. M. (2004). The impact of scaling on metal thickness for advanced back end of line interconnects. Thin solid films, 469, 487-490. [2] van der Veen, M. H., Heyler, N., Pedreira, O. V., Ciofi, I., Decoster, S., Gonzalez, V. V., … & Tőkei, Z. (2018, June). Damascene benchmark of Ru, Co and Cu in scaled dimensions. In 2018 IEEE International Interconnect Technology Conference (IITC) (pp. 172-174). IEEE. [3] Techinsights TSMC 5nm logic tear down report. [4] http://www.coventor.com/products/semulator3d