作者:电子创新网张国斌

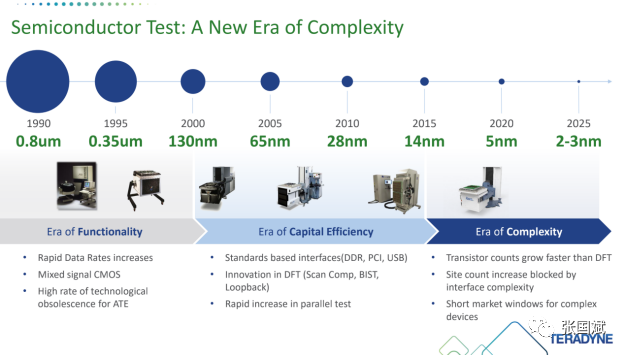

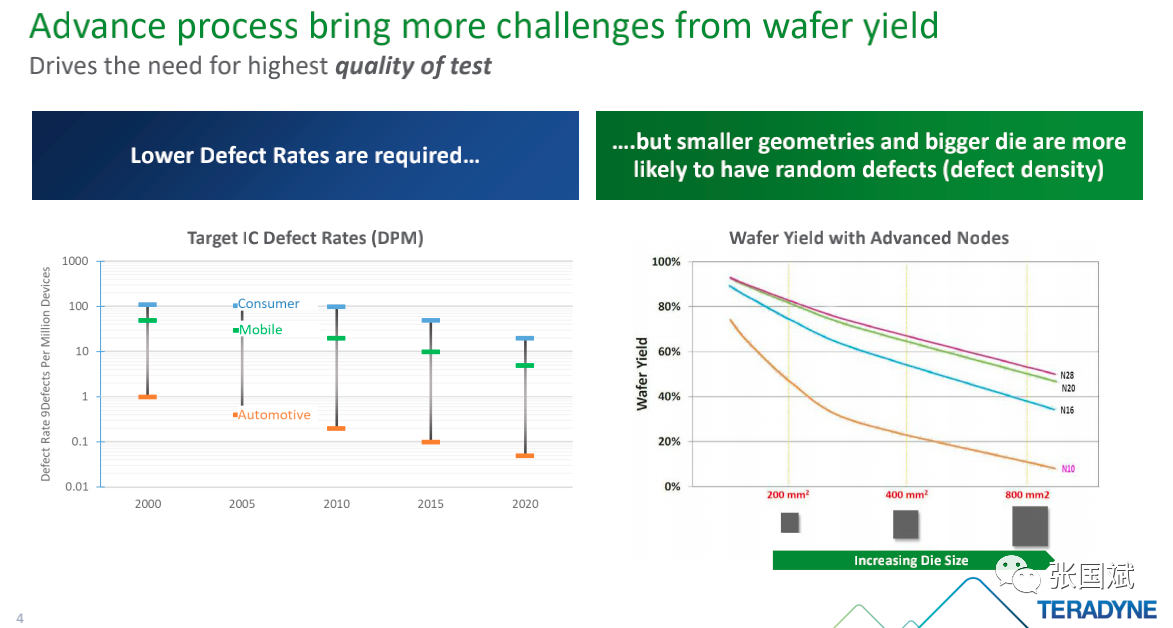

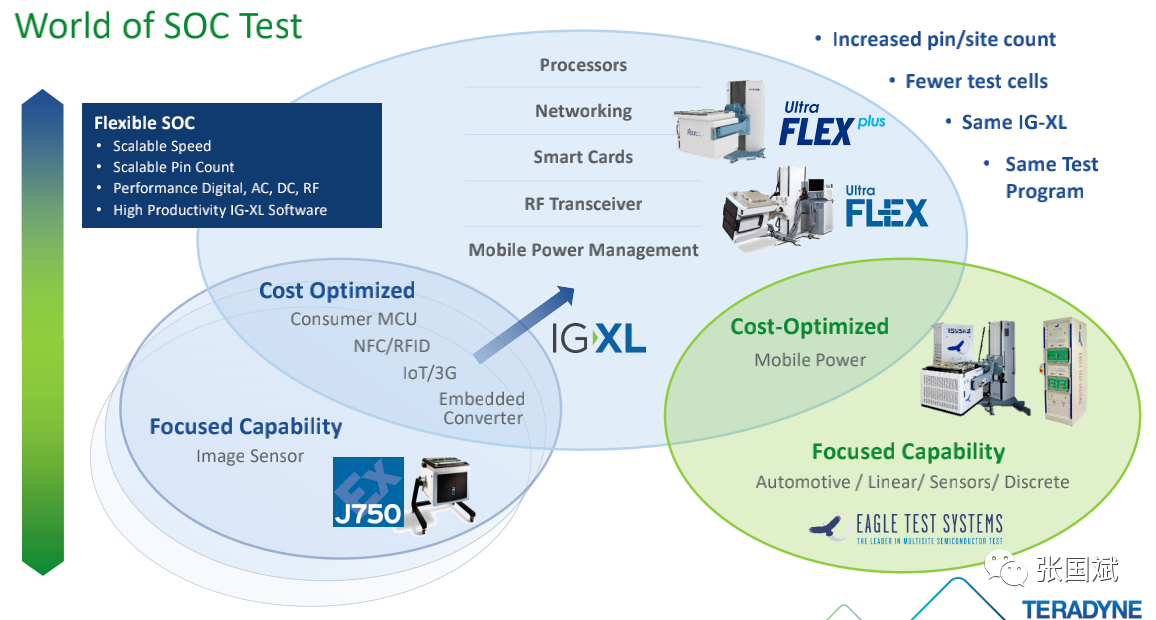

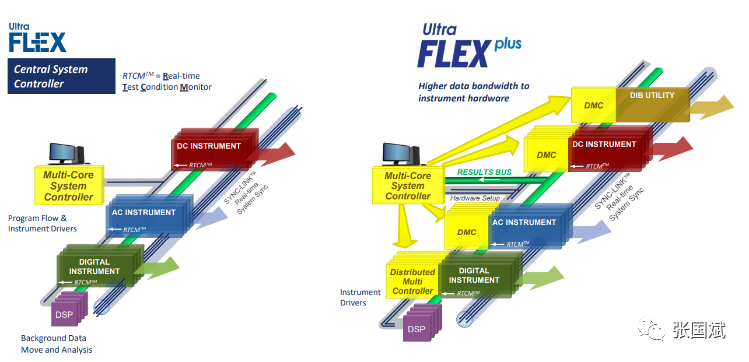

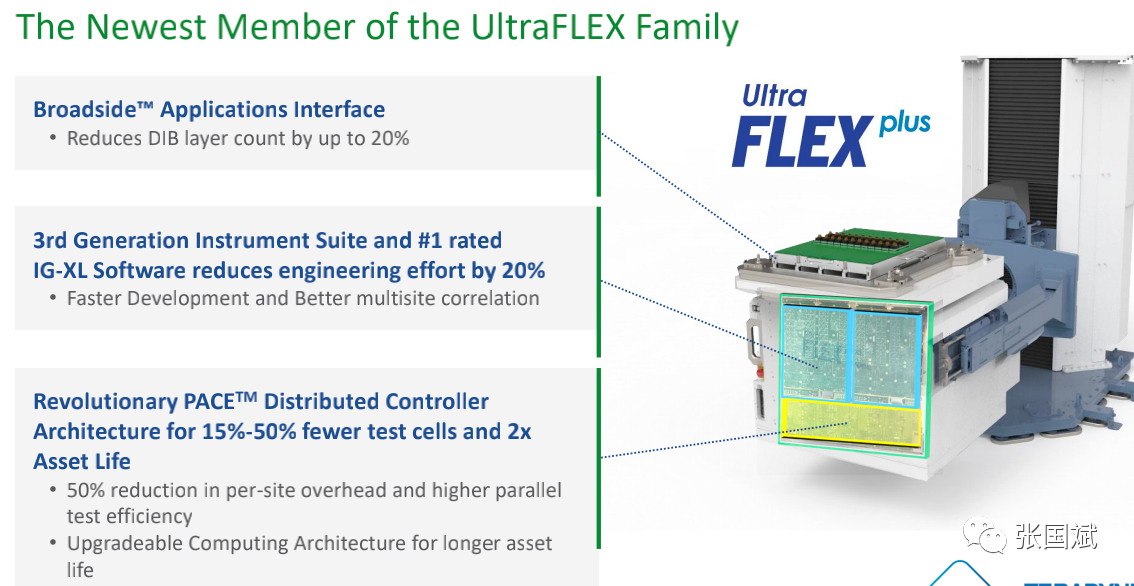

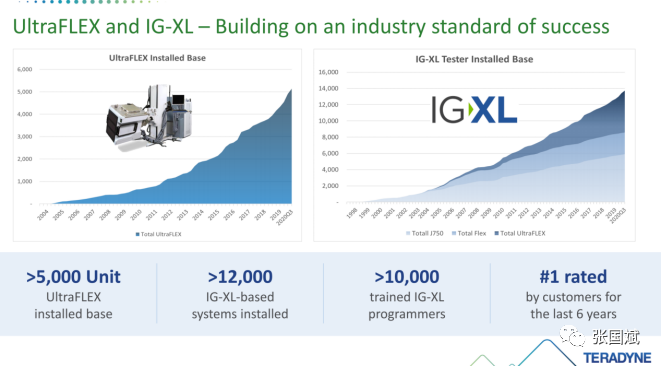

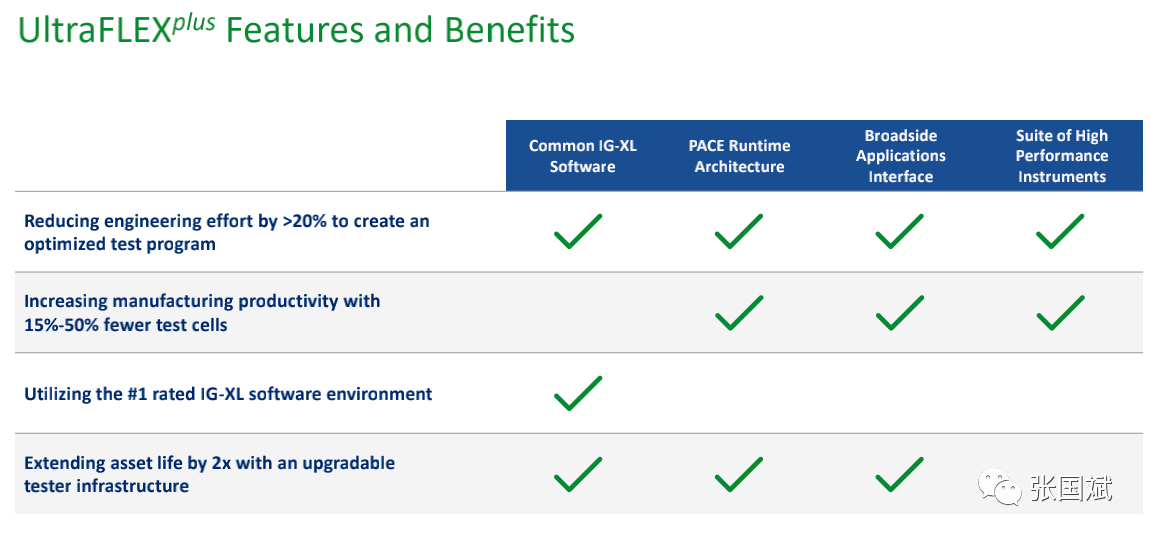

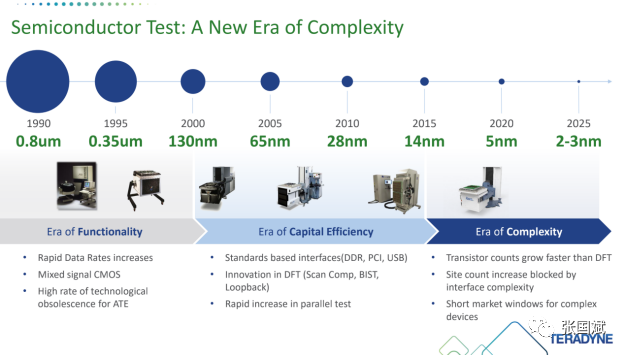

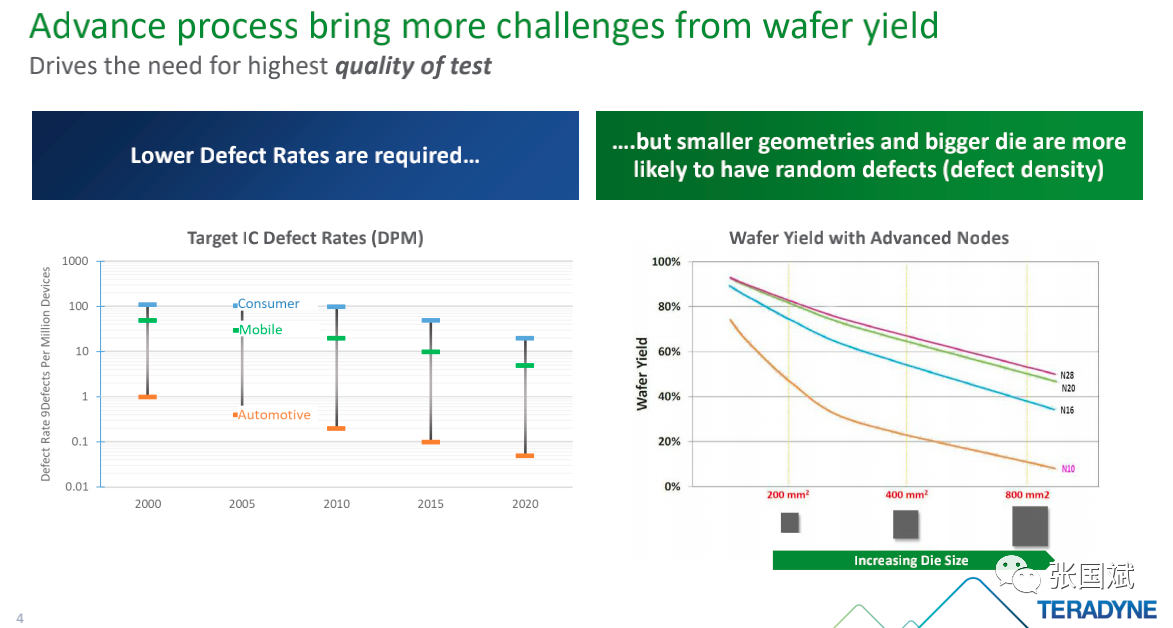

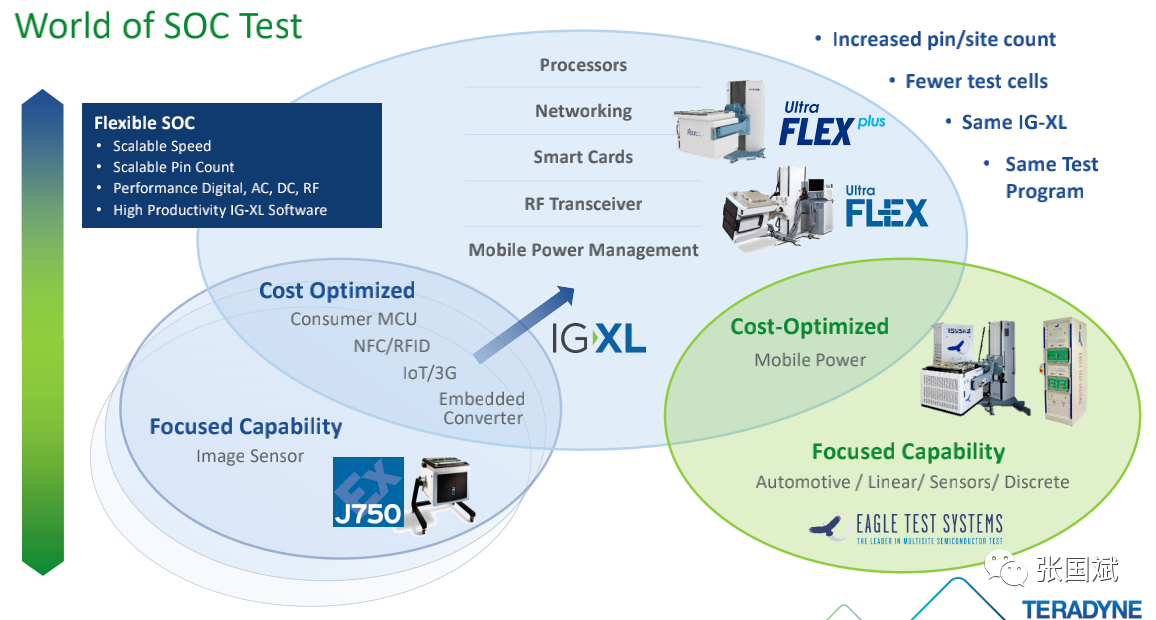

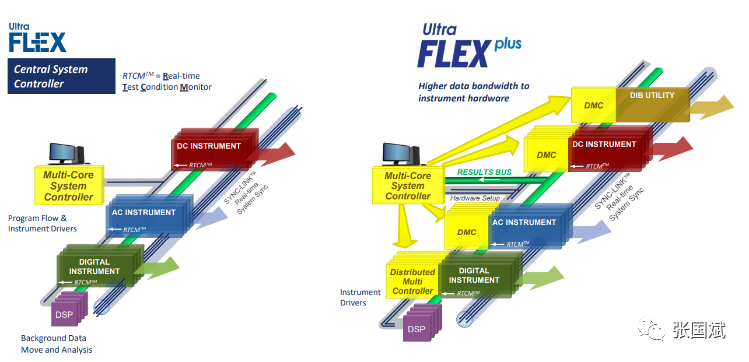

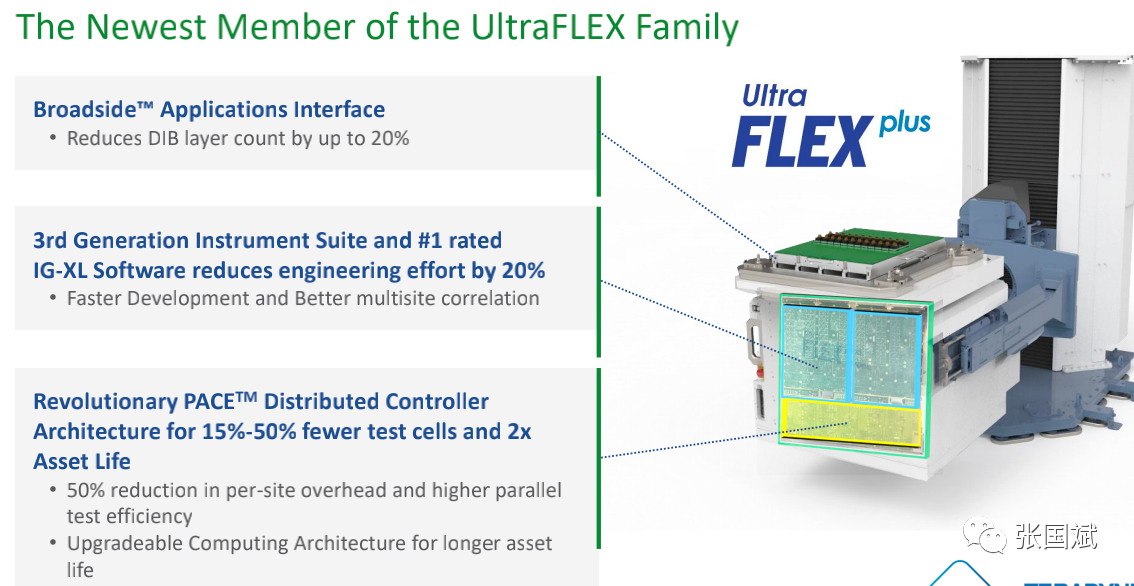

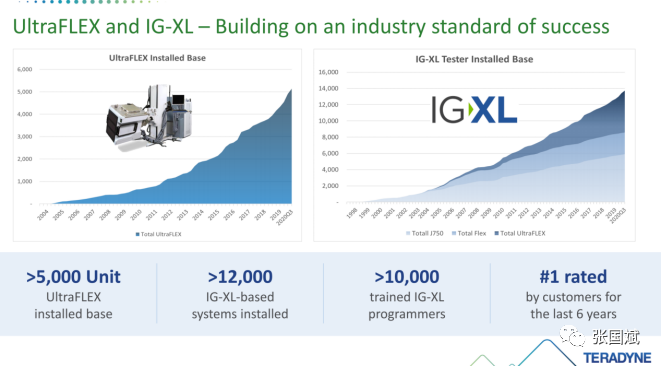

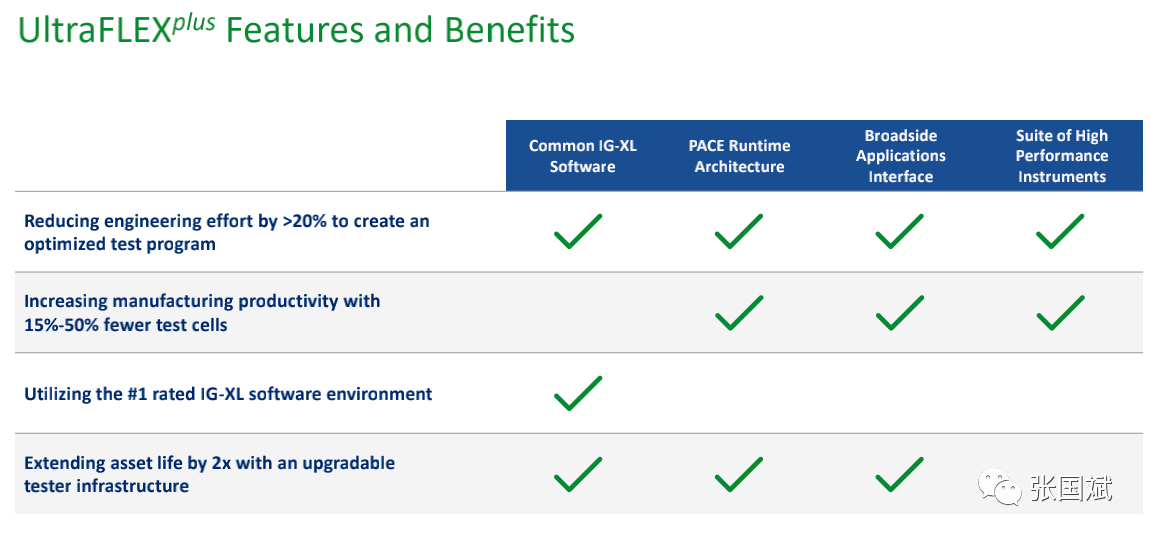

近年来,5G技术已进入爆发期,人工智能技术初露锋芒,物联网、智能家具设备也逐步进入大众的视野中,各种新应用的兴起也推动了半导体市场的蓬勃发展,整体芯片需求呈现爆发增长的态势。在供不应求的缺芯大环境下,使晶圆产能急剧扩张,包括ATE在内的半导体设备总需求量也随之增加。近日,在泰瑞达(TERADYNE)的媒体沟通会上,泰瑞达中国区销售副总经理黄飞鸿为媒体们回顾了芯片测试设备的发展历史,并对其未来做出了展望。黄飞鸿表示从发展历史来看,芯片测试设备经历了三个发展阶段,分别是功能性时代、资本效率时代和复杂性时代。三个阶段如下:上世纪90年代,随着CMOS工艺的迅速发展,SoC芯片的功能愈发强大。芯片的集成模拟的能力、包括数据接口的传输率也在同步增加。传统测试平台已不能满足新生的模拟和高速接口测试需求,为满足日趋复杂的SoC芯片测试需求,ATE测试机开始了功能性扩展,我们称这个时代为“功能性时代”。到了2000-2015年,芯片制程开始向90nm、65nm、28nm和14nm演进,芯片尺寸越来越小,芯片上面晶体管的集成度却越来越高。随着芯片的复杂度进一步加剧,芯片测试也成为芯片成本中的重要支出。为此,供应商纷纷开发出支持多工位并行的机台,增强自身的同测能力,提高效率。并开始加强ATE测试机的标准化接口和DFT设计测试能力,从而满足扫描、BIST和标准化接口测试的需求。我们称这个时代为“资本效率时代”。2015年之后,半导体工艺逐渐下探至2-3nm,此时DFT技术已经无法跟上晶体管的增长幅度,而且机台工位数也不允许无限制扩大。而同时,随着竞争的加剧,产品的上市周期要求不断缩短的同时,生命周期也在缩短。因此在这一系列要求的叠加下,测试产业进入到“复杂性时代”。他表示随着先进工艺的演进,芯片工艺尺寸越来越小,各类芯片功能越来越多,芯片复杂度水涨船高。这一系列因素导致工程师在对芯片进行校准、修复和测试时所需的步骤大大增加。此外,随着晶体管数量的增加,满足最低质量标准所需的故障覆盖率也成为了一个巨大的挑战。且如物联网、智能家居、 5G和AI等新应用的产品芯片生产厂家,也亟需一个可满足复杂测试需求、能灵活应对各种芯片进行测试的平台。泰瑞达产品家族新晋成员——UltraFLEXplus这次发布会上,泰瑞达介绍了其家族新成员---UltraFLEXplus,黄飞鸿表示泰瑞达聚焦解决人工智能和5G通信所带来的新兴数字测试需求,于2019年推出全新测试设备——UltraFLEXplus,UltraFLEXplus将 IC 量产所需的测试单元数量减少了 15%-50%,并通过减少多工位测试时间开销来提高并行测试效率,从而满足日益复杂的测试需求。 当前,测试特性分析需求和量产数据量的增加,已逐渐挑战到当前测试机架构的极限。这无疑会导致开发周期的延长以及量产测试时间的增加。为了应对这一新兴挑战, UltraFLEXplus创新地使用了PACE 多控制器架构。这种革命性的技术,使测试工程师能够更高效地对复杂芯片进行调试和特性分析,实现更少的工作量和更高的测试机利用率,将新产品更快推向市场。据介绍,UltraFLEXplus 上的“Broadside”应用接口简化了 DIB 布线设计,改善工位间结果一致性,并通过简化原本复杂的 DIB布局,实现更高的PCB良率。而IG-XL 软件、独有的 PACE 架构和 Broadside 应用接口的完美结合,更是保证了测试程序的可全面兼容,使得测试工程师能够以更少的工作量将新测试程序发布到量产环境,从而加快产品上市时间。 目前,IG-XL软件平台装机也超过了12000套。自问世以来,UltraFLEXplus全球装机量也已经接近600套,已在两家主要晶圆代工厂以及5家OSAT安装使用,得到了获得市场的检验和客户的广泛好评 。随着工艺节点向3nm、2nm演进,芯片的晶体管数量呈现几何数级的增长,这给芯片测试系统带来了巨大的挑战,针对这个趋势,黄飞鸿表示从14纳米到5纳米到2纳米,以AP芯片来说测试内容并没有太大的变化,只是测试时间会更长,另外跑向量的时候,这个深度是越来越深了。“CP测试和FT测试,从工艺不断演进到往后有一个趋势,wafer测试比重会增加,FT测试反而会减少,因为工艺演进技术有两条路,一条路是5纳米,2纳米,1纳米不断往前走,但其实演进难度越来越难了。另外一条是Chiplet(芯粒),也就是一颗芯片里面不同的模块不一定每个模块芯片都需要用到2纳米,3纳米,有些射频、模拟、混合信号需要16纳米就够了,所以现在是把不同功能的一颗一颗芯片(Die),在片上再把它合封在一起,封在一起其实是没法测了,因为你不会把所有管角引出来,那对于芯片来说CP比重会增加,FT会减少。”他指出,“后面可能会有一个趋势,合封之后也有通讯组件的标准,它的标准怎么样通过外围共用的通道access到每一个die去,目前还没有特别好的统一的标准。这个如果这个标准出来,可能也会通过这个方式访问到每个芯片(Die)再进行测试。这里面带来另外一个问题,其实在晶圆测试这块每个Die都测的很好,合封的时候也有可能带来失效率怎么办?还有一道不在我们这儿,我们公司还有另外一块产品SLT(系统级测试),整颗芯片出来,比如说放到手机上面的芯片,它是有PCB小板,验证板,我整机放上去连着小板一起测,这是最贴近于实际芯片场景的测试。一个芯片从die开始到封装到测试是三道,有一种趋势是哑铃型的。我们现在说法叫百百测,百分百测试,每一个芯片都要测试。”芯片测试作为集成电路产业链重要一环未来有巨大的发展潜力,数据显示集成电路测试成本约占设计营收的 6%-8%,假设取中值 7%,结合中国半导体行业协会关于我国芯片设计业务的营收数据测算,2019 年我国集成电路测试市场规模为 214 亿元,同比增长 22%,2020 年我国集成电路测试市场规模为 264 亿元,同比增长 23%。2021 年中国我国的测试服务市场规模为 300 亿元,全球的市场规模为 892 亿元。2025 年,预期全球测试服务市场将达到 1094 亿元,其中,中国测试服务市场将达到 550 亿元,占比 50.3%,5年内存在超过 250 亿元的巨量增长空间。在泰瑞达领头羊的带领下,本土芯片测试企业也在快速发展,专注芯片测试的利扬芯片在2020年上市,据悉,2022年也将有本土芯片测试设备厂商也将开启IPO,芯片测试大有可为!(完)注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利!