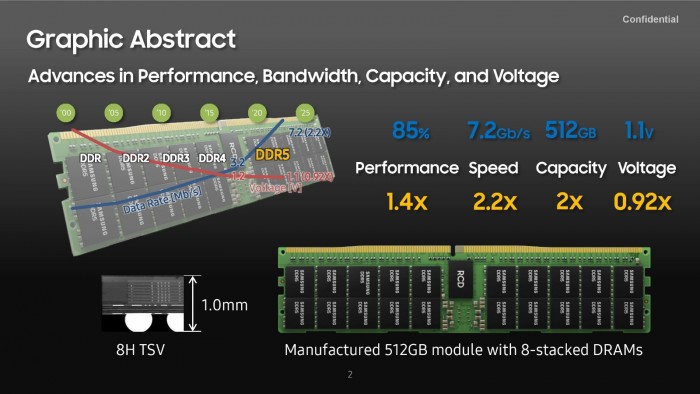

在近日举办的年度 Hot Chips 半导体会议上,三星内存部门在一份 PPT 中,详细介绍了他们在 DDR5 内存模组上取得的最新进展。其中包括了一款单条容量 512GB 的 DDR5-7200 内存模组,可知其专为服务器和企业级应用而设计,较当今市面上高端的 256GB 内存模组更进了一步。不过为了实现这一目标,该公司还引入了一些新的功能特性。

AnandTech 指出,DDR5 内存模组的标准运行电压为 1.1 V 。而三星的单条 512GB 内存模组,也遵循了标准的 JEDEC DDR5-7200 时序。

需要指出的是,JEDEC 尚未正式颁布 DDR5-7200 标准,而是只有 DDR5-6400 。不过未来应该还有 DDR5-7200 等占位,预计时序在 50-50-50 到 60-60-60 之间。

此外每个 DDR5 标准都提供了 -A、-B、-C 三个衍生版本,比如 DDR5-6400A 的时序为 46-46-46 ,但 DDR5-6400C 的时序就放宽到了 56-56-56 。

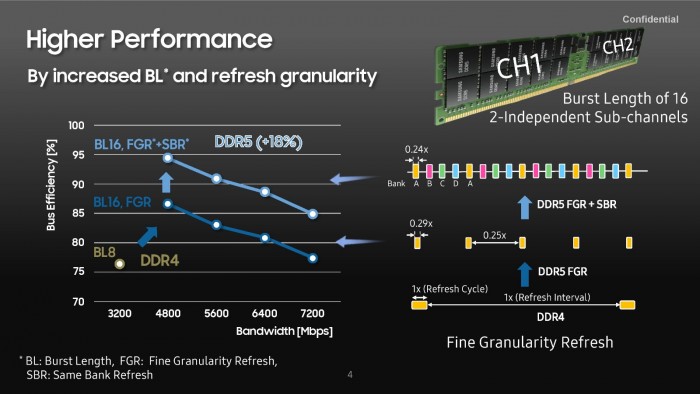

作为演示的一部分,三星表示在其 DDR5 内存模组中引入了 Same-Bank 刷新(SBR)技术,从而将 DRAM 总线连接的效率提高了近 10%(辅以特定频率下的最佳能效表现)。

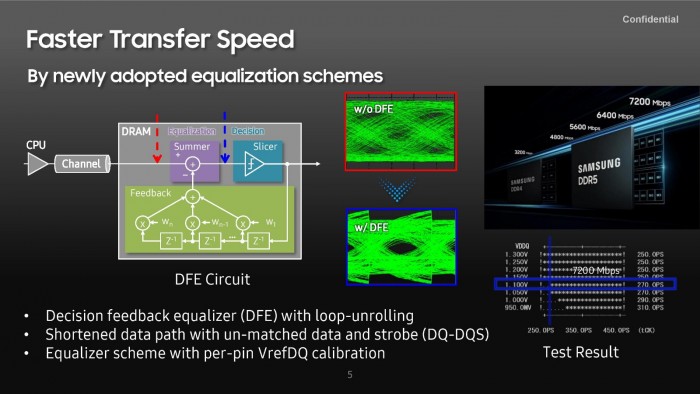

其次,为支持 DDR5 更高的内存传输速率,三星还推出了新的决策反馈均衡器(DFE)以获得更好的信号稳定性。其允许更多可变的数据路径位置,以及每引脚校准技术。

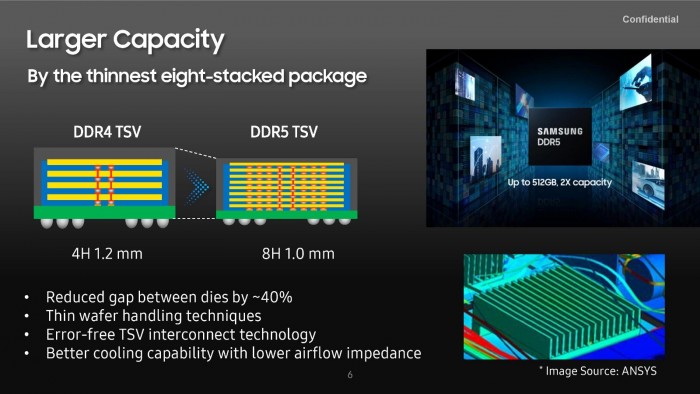

增加内存容量的一大好处,就是可将更多的内存堆叠到一起。以三星为例,该公司称可将 8 颗 DDR5 芯片堆叠到一起,同时占用小于 4 颗 DDR4 芯片的空间。

显然,这得益于减少每个裸片的厚度、以及新颖的硅通孔连接拓扑结构而实现。这些拓扑结构可将裸片之间的间隙减少多达 40%,结合有助于提升散热表现的新技术。

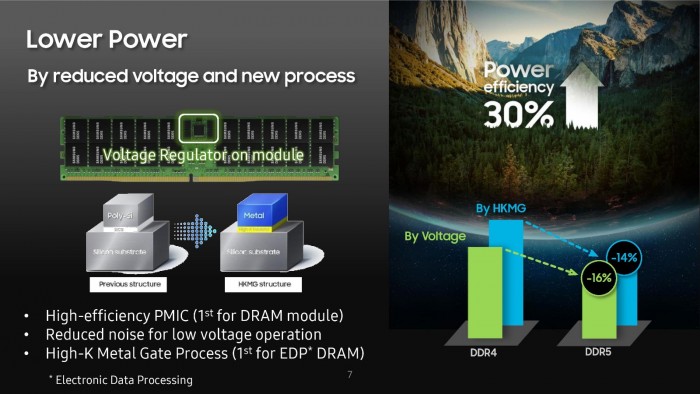

供电方面,我们得知为了进一步降低电压与功耗,JEDEC 新标准还将电源管理芯片(PMIC)从主板端挪到了 DDR5 内存的 PCB 上。

这不仅使得内存模组制造商能够更严格地控制内存的供电需求和消耗,还使得 DDR5 内存可在电压调节能力上摆脱廉价主板的缩水困扰。

以三星 512GB DDR5 内存为例,其使用了更加高效的 PMIC 芯片。作为一家行业龙头企业,该公司电子部门拥有丰富的设计经验。

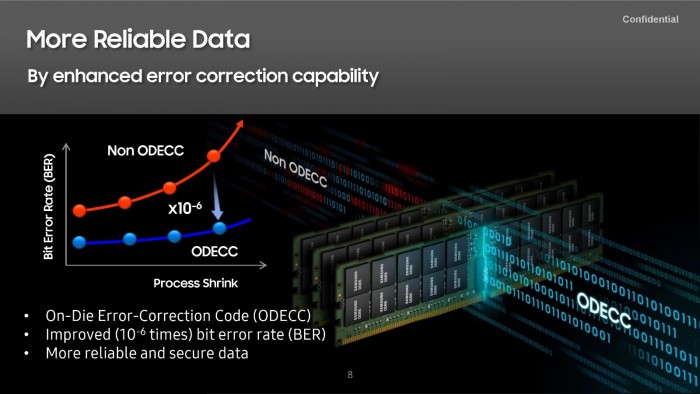

板载 PMIC 不仅有效降低了噪声影响,还使之能够在较低的电压下运行。此外 DDR5 内存模组已标配片上 ECC(ODECC)校验功能。

需要指出的是,这并不是在 DDR5 内存模组上真正启用了 ECC 功能,因为它仍需借助额外的物理内存和受保护的总线。即便如此,三星还是宣称将误码率(BER)降低到了百万分之一(10^-6)。

在演示文稿的末尾,三星指出首批 512GB DDR5 内存模组有望在 2021 年底前做好量产准备。至于是否为 DDR5-7200 的规格,目前暂不得而知。

最后,三星预计 DDR4 / DDR5 内存市场的代际交替将于 2023 ~ 2024 年间发生,这与其它分析师的预测保持一致。

来源:cnBeta.COM