作者:电子创新网张国斌

在过去三十年里,EDA 行业的进化方式几乎是“反 AI 直觉”的——算法演进、流程高度工程化、核心能力牢牢绑定在人类专家的经验上。

这是一个对“黑盒”天然警惕、对确定性极度苛刻的行业。

但现在,这条延续了数十年的技术路径,正在被 AI 强行改写。

而更值得警惕的是:这并不是一次简单的效率提升,而是一场被严重低估的产业级范式变革。

在1月8日贸泽电子芯英雄联盟直播间,深圳鸿芯微纳技术有限公司副总裁冯春阳博士分享了EDA与AI融合的大趋势,并与众多网友互动,探讨了EDA与AI融合的技术细节。

一、EDA与AI融合第一阶段已经结束

冯春阳博士表示,目前,“给 EDA 加点 AI”,已经是过去式,过去几年,行业谈论“AI+EDA”,大多停留在点状优化:

用机器学习调 P&R 参数

预测 DRC hotspot

加速时序收敛

提前估算功耗、拥塞、风险点

这些方法有没有价值?有,而且价值不小。但它们有一个共同特征:不改变设计范式,只是在既有流程上提速。

EDA 的角色没有变,工程师的工作方式也没有变,AI 只是“更聪明的助手”。

这一阶段,已经结束了。

真正的转折点要来了,AI 正在进入“设计决策层”

当前正在发生的,是第二阶段。

EDA × AI 的角色,正在从局部工具优化器,“跃迁为跨阶段、跨目标、跨约束的设计决策参与者。”他指出,“一个极其重要的变化是EDA 正在从 Tool-level,走向 Flow-level AI。AI 不再只参与 placement、CTS 或 routing 的某一个环节,而是开始跨越:

架构选择

工艺节点评估

IP 组合策略

芯片/封装协同路径

优化目标,也从单一指标,升级为PPA + 成本 + 风险 + 设计周期 的全局最优

这意味着什么?这意味着工程师不再只是“调工具”,而是开始与系统共同决定设计路径本身。

二、生成式 AI,已正式进入 EDA 主流程

很多人低估了生成式 AI 在 EDA 的落地速度。但事实上,它已经进入主流程的多个关键层级。

1️⃣ RTL 与 IP 层

自动生成模块骨架

参数化 IP 组合

接口、时钟域、复位逻辑自动补全

2️⃣ 约束与脚本

自动生成 SDC / UPF / TCL

学习团队历史项目的设计风格

降低“隐性工程规范”的学习成本

3️⃣ 工程管理与 Review

自动生成设计说明

提炼 Review 重点

分析设计变更的连锁影响

一个关键转折点正在发生:芯片设计,正在从“人写代码”,转向“人定义目标,AI生成,人工审核”。

三、强化学习,正在重构 PPA 优化的底层逻辑

如果说生成式 AI 改变的是“输入方式”,那么强化学习(RL)改变的,是 PPA 优化的底层机制。

核心应用场景已经非常清晰:

Floorplan 探索

Placement 密度与拥塞控制

CTS 策略选择

多目标 trade-off(功耗 / 频率 / 面积)

为什么 RL 特别重要?

设计空间指数级爆炸,人工调参不可持续

高阶工艺的“隐性经验”难以显式建模

新工艺节点 learning curve 极长

冯博士指出强化学习的本质,是把“不可穷举的工程经验”,转化为可学习、可迁移的策略。产业影响极其直接:高端工艺节点的经验壁垒,第一次被系统性削弱。

四、STCO 与 3DIC:

冯博士表示把 EDA × AI 推向系统级战场,真正放大 AI 价值的,是 Chiplet 与 3DIC。新时代的设计难题已经发生质变:

Die-to-Die 互连复杂度激增

热–功耗–时序强耦合

工艺、架构、封装高度联动

这些问题,已经超出了传统 EDA 的线性能力边界。

AI 的新角色正在成型,就是多物理场联合预测、Chiplet 拆分方案自动探索以及封装形态与 SoC 架构协同搜索

可以明确判断,“STCO,将成为 AI-EDA 最重要的主战场之一。”他强调。

五、EDA融合AI 的终极形态:

EDA融合AI正在进化为“设计智能体(Design Agent)”,一个极其关键、却常被忽略的趋势是EDA 正在从“工具”,演进为“设计智能体”。

设计智能体具备什么能力?

理解设计目标

调用多种 EDA 工具

执行完整子流程

在失败后自我修正

未来可能出现的形态包括:

架构探索 Agent

时序收敛 Agent

功耗优化 Agent

封装协同 Agent

其本质只有一句话:把工程师的隐性经验,转化为可复制、可迁移的系统能力。

主持人电子创新网CEO张国斌指出在AI 时代,EDA 的护城河正在重写,传统 EDA 的护城河是:算法、工具链和客户粘性,而在 AI 时代,真正稀缺的变成了真实设计数据、工程决策数据以及跨节点、跨产品的经验迁移能力。

这正在引发三种趋势:

大厂自研 AI-EDA

Foundry 与 EDA 深度绑定

开源工具 + 私有数据混合训练

所以,EDA 的竞争维度,正在发生结构性变化。

六、国产 EDA 的机会,正在打开

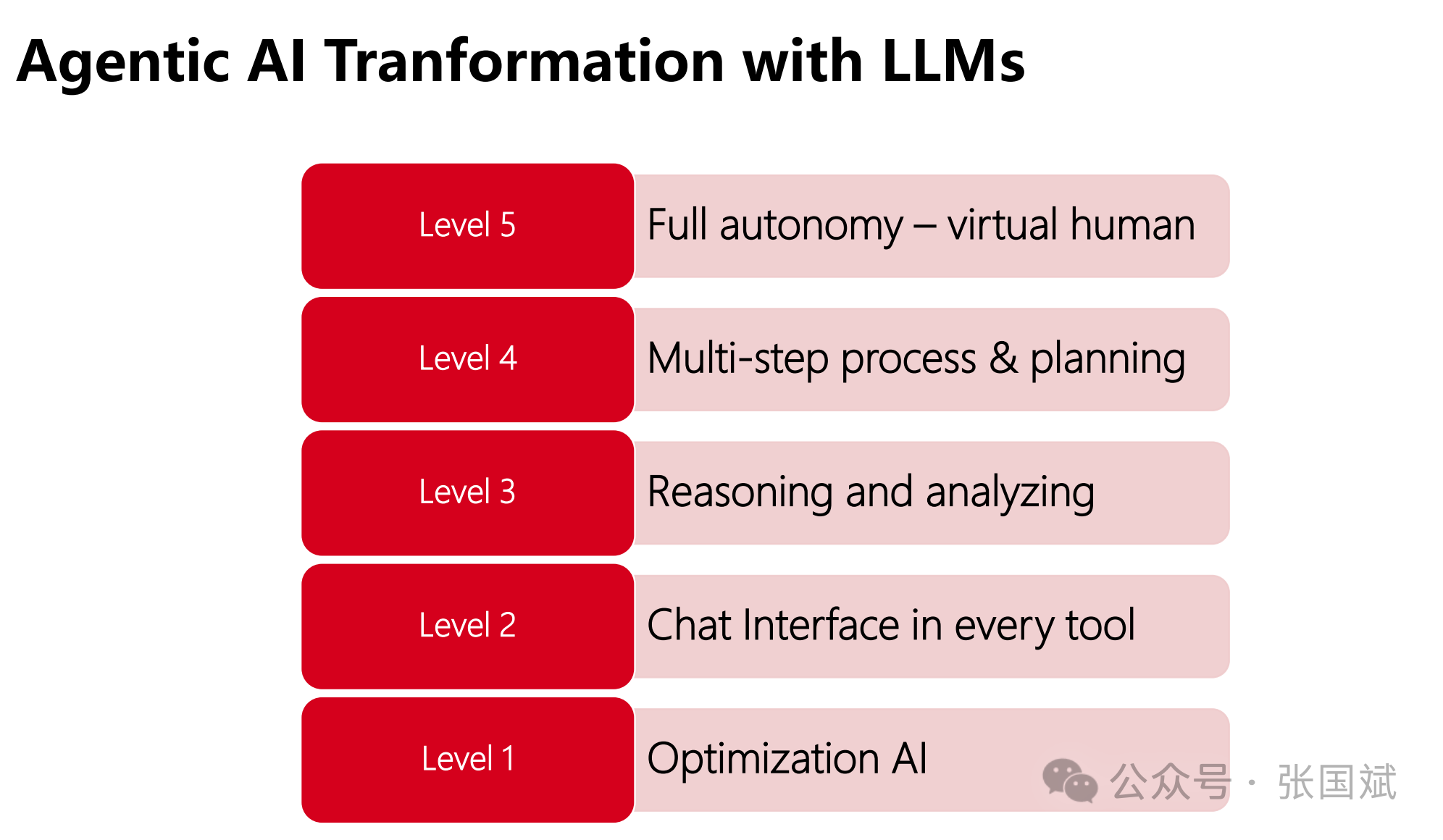

冯博士表示利用大语言模型实现EDA智能体实际上也分五个层级,最高层级就是实现虚拟人交互全自动设计---就是识别自然语言自动设计出芯片,但是这个最终层级还需要时间,目前业界已经走在L3 ,他预测2026年会有L4级的智能体出现。

对于本土EDA来说,AI 不会自动抹平差距,但它确实改变了竞争规则。这对于本土EDA来说机遇与挑战并存,谁先把 AI 嵌入设计流的“核心决策层”,谁才有资格谈国产 EDA 的真正破局。

所以,这不是工具升级,而是设计范式重构,EDA × AI 的终局,从来不是“更聪明的工具”。而是:从工程师个人经验驱动,走向系统级、数据驱动、智能体协同的芯片设计范式。

这场变革,刚刚进入真正的深水区。

冯博士还总结说很多人担心AI会抢走自己的饭碗,“实际上,AI会让人强的人更强,只要你善于利用AI ,则你的设计效率会大大提升!”

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利