作者:电子创新网张国斌

在RISC-V快速扩张的浪潮中,SoC设计正变得越来越复杂,调试环节面临前所未有的挑战。如何精准还原隐性Bug、快速分析系统瓶颈、保障自定义逻辑的正确性,已成为RISC-V生态走向成熟的关键。在2025RISC-V中国峰会上,西门子EDA 客户技术经理李一凡介绍了西门子EDA最新推出的Tessent UltraSight-V,它正是在这个背景下应运而生,为嵌入式系统开发者带来面向未来的调试与追踪解决方案。

01 调试困境正在逼近:RISC-V SoC的“黑盒危机”

“调试,越来越贵,越来越难。”——这是李一凡在演讲开场时的第一句总结。这并非危言耸听。随着RISC-V SoC集成度大幅提升,软件与硬件交互日益复杂,调试的重点早已不再是单核寄存器级别的简单问题,而是跨多核、跨模块、甚至跨Chiplet的系统级观测与分析:

多核系统状态无法一致可见;

Heisenbug(观测即改变)和Anomaly Bug难以复现;

Silent Data Corruption(静默数据错误)根本无法感知。

在这种“黑盒化”日益严重的趋势中,构建可观测性更强、可压缩性更高、集成更轻量的调试追踪体系,成为下一代调试架构设计的关键。

02 三个关键模块:构建完整片上调试子系统

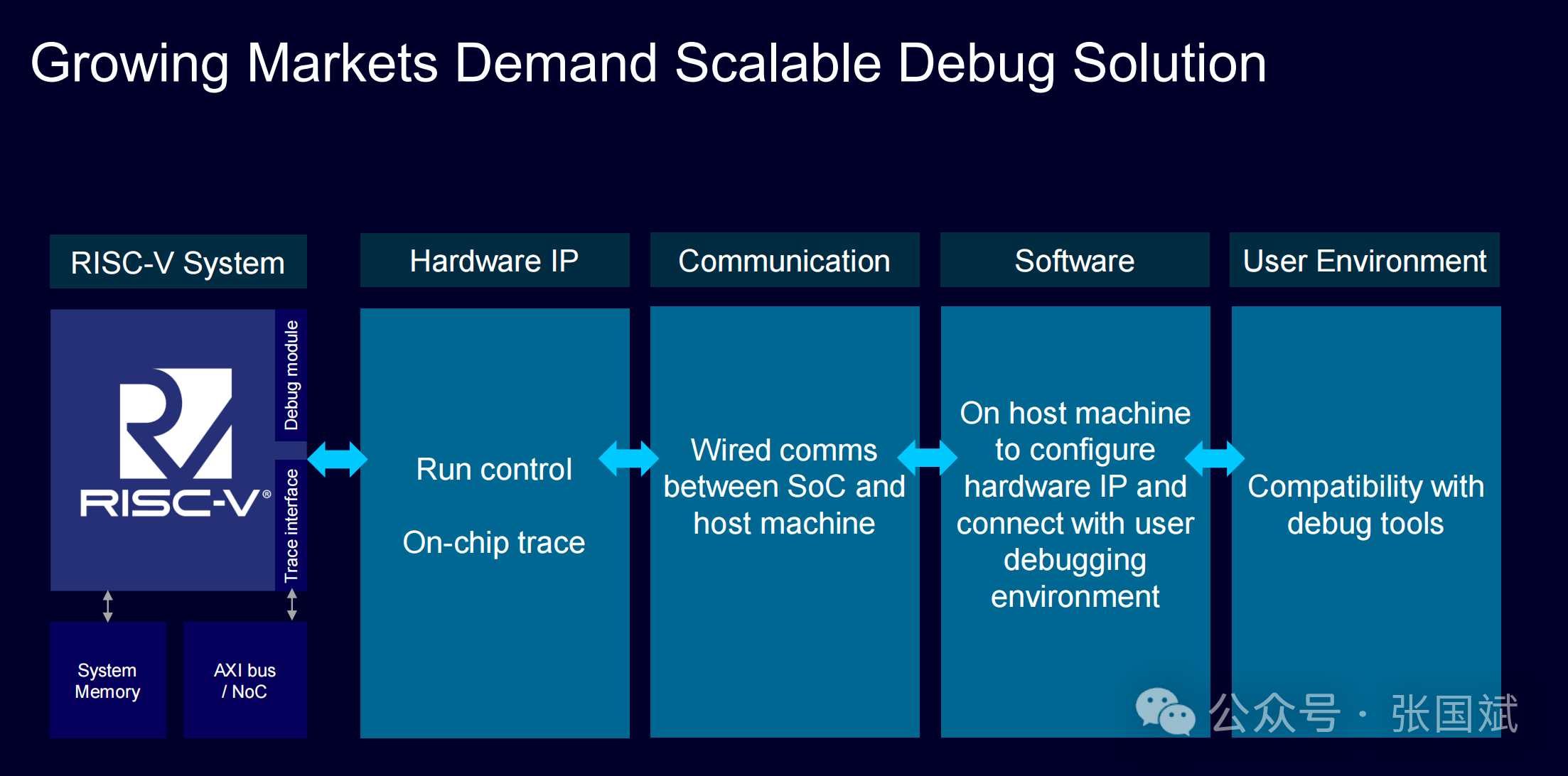

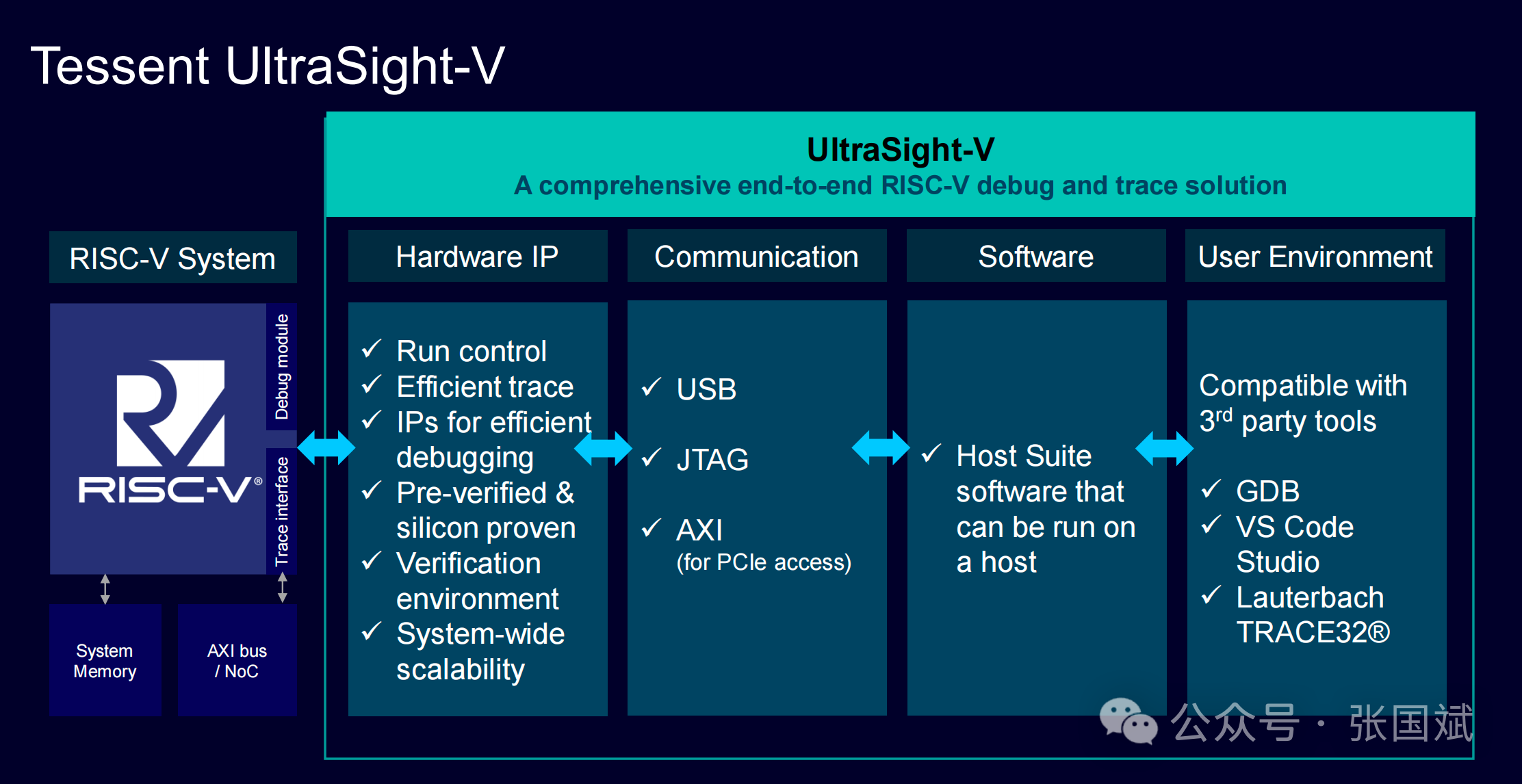

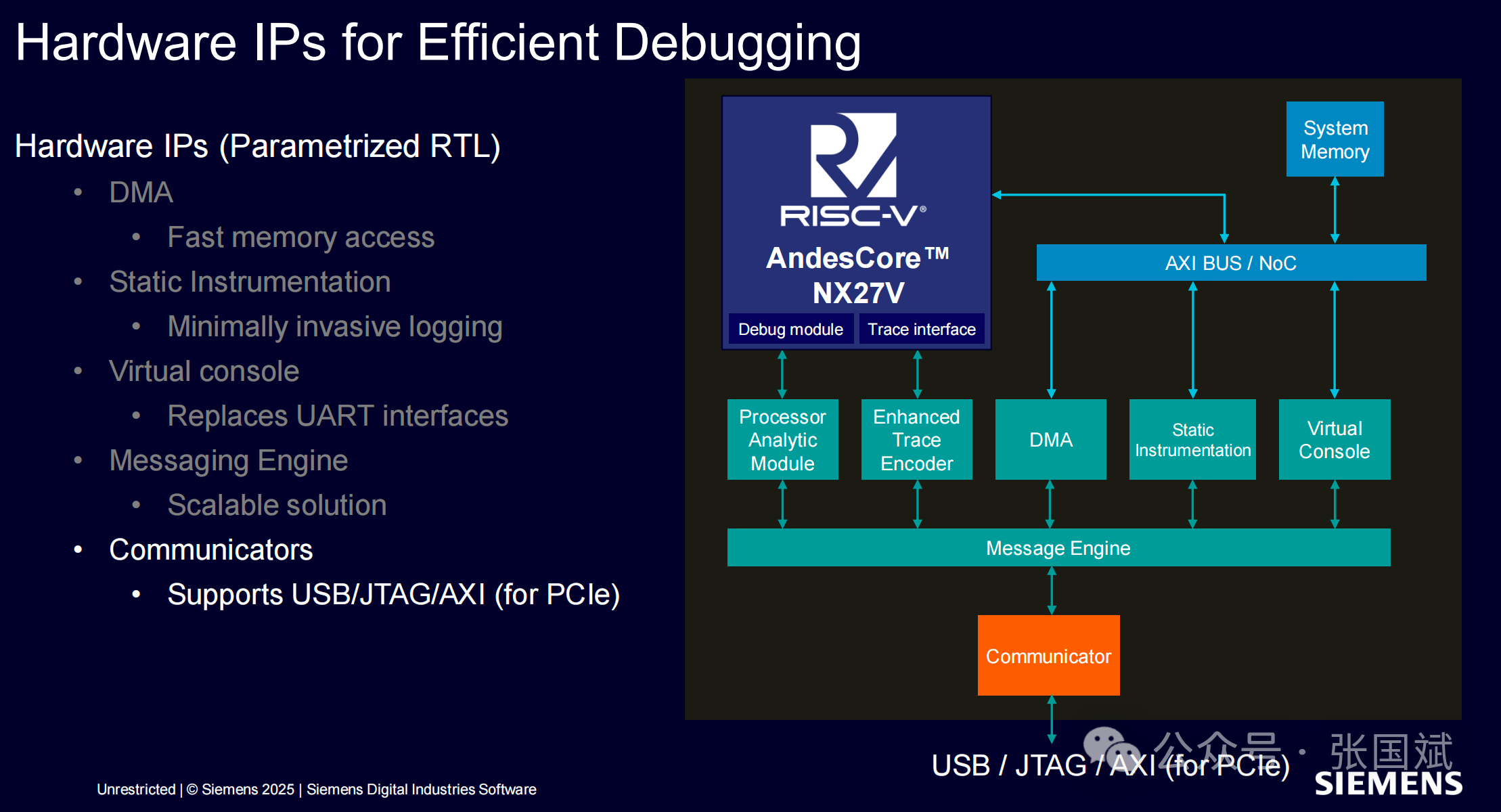

针对RISC-V SoC的调试特性,UltraSight-V以模块化架构思路构建出“硬件调试控制 + Trace追踪 + Host通信接口”三位一体的片上调试平台:

运行控制模块:支持多核暂停、恢复与断点控制;

Trace数据通路:实时捕获处理器状态及总线行为,可压缩、可筛选;

主机通信接口:通过USB、PCIe等方式与调试上位机交互,并支持主流IDE和调试工具(如GDB、VS Code)。

此外,该方案对第三方IP高度兼容,可快速接入各类SoC平台,显著降低开发者集成门槛。

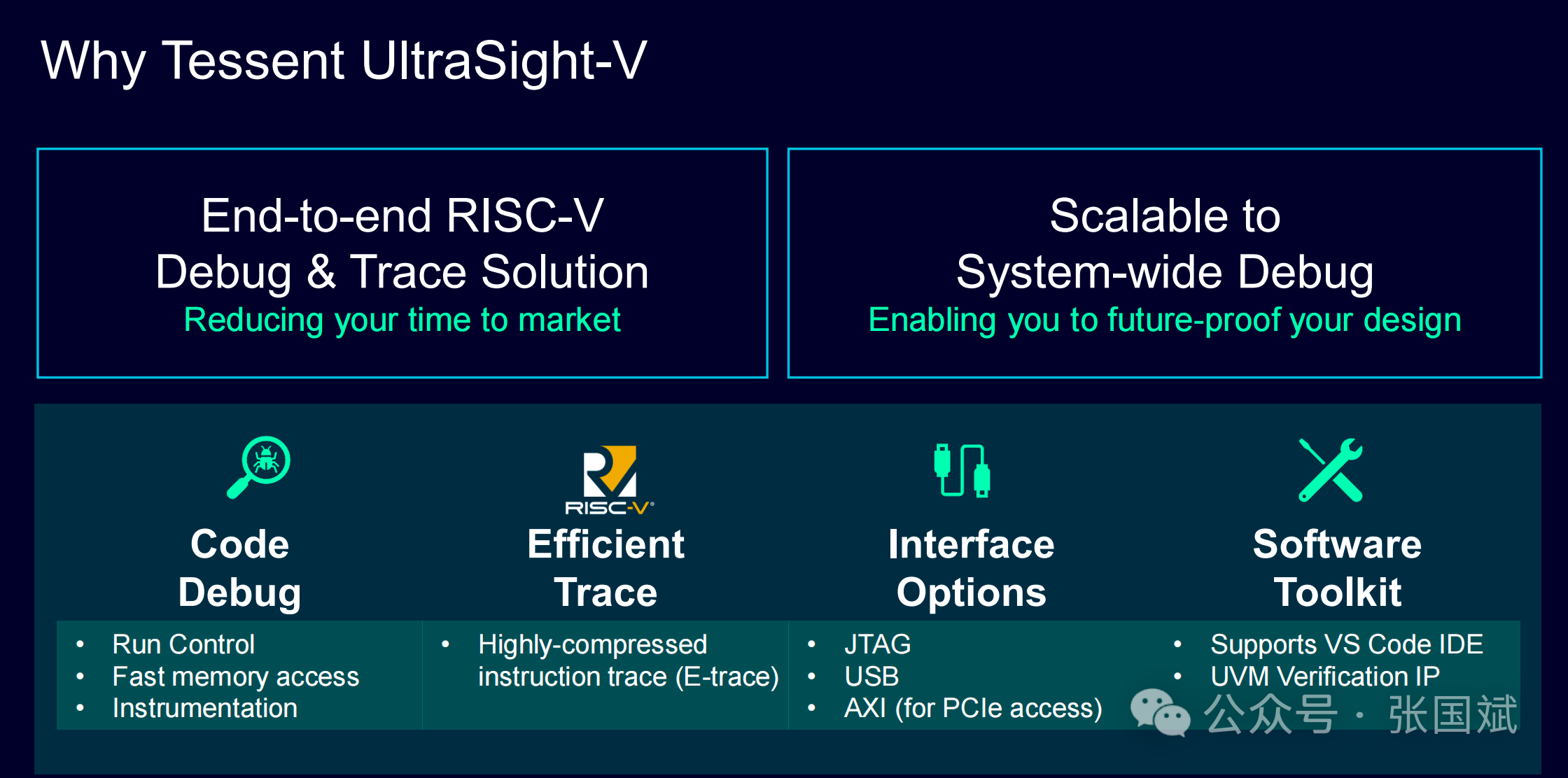

03 可扩展、可压缩、可集成:UltraSight-V三大核心优势

01|极致压缩率,Trace带宽节省高达40%

UltraSight-V的Trace数据采用先进的可配置压缩机制。李一凡展示的一组数据表明,在开启拓展压缩选项后,平均比特数(BPI)下降了40%,在同样带宽与存储条件下,可以记录更长时间的行为轨迹,显著增强调试覆盖能力。

02|支持RISC-V自定义指令扩展

RISC-V强调灵活性,自定义指令频繁出现。但这也成为传统调试方案的“盲点”。UltraSight-V提供可扩展调试库机制,允许用户通过API扩展调试逻辑、分析RISC-V自定义指令行为,真正做到对用户定制CPU架构的“白盒”观察。

03|多核/多线程/多芯片支持,追踪分布式系统Bug

UltraSight-V不仅支持单核调试,还具备完整的多CPU协同跟踪能力,可对多线程应用中的调用栈、同步点进行可视化分析,助力开发者发现复杂的Race condition与跨核同步问题。同时,系统也已拓展到Multi-Die系统调试能力,连接多个SoC子系统统一监控,满足Chiplet架构下的调试需求。

04 全流程工具链支持:从代码调试到系统分析

西门子EDA并非仅提供硬件IP,而是构建了一整套端到端的调试链条:

硬件层面:Tessent调试IP(包括PAM、E-Trace、DMA等)构成数据抓取主通路;

验证层面:提供UVM VIP及接口验证工具,确保调试模块与SoC无缝连接;

软件层面:支持标准调试工具(GDB、VS Code)、支持RISC-V拓展解析、支持性能分析插件;

数据分析层面:Host Suite可进行调试信息收集、可视化、日志重构与错误追溯。

值得一提的是,调试信息可以实时送达开发主机,结合GUI界面与命令行工具,开发者几乎无需中断系统运行,即可动态调试代码,大幅提升开发效率。

从微观看,UltraSight-V可以帮助开发者迅速定位Bug、优化代码、验证功能;从宏观看,Tessent UltraSight-V构建的是一个面向系统级调试的生态闭环:

第一阶段:Code-Level Debug,支持基本软件调试;

第二阶段:SoC-Level Debug,支持片上多核/异构系统调试;

第三阶段:System-Level Debug,支持Chiplet与Multi-Die系统调试;

第四阶段:Cross-System Debug,目标拓展至车载、云端、工业级系统的多模块联合调试。

西门子EDA不仅是调试IP的提供者,更正在成为复杂系统可观测性的基础设施提供者。

结语:让专业的工具,做专业的事

如李一凡在演讲中所言:“让专业的人、专业的公司来做专业的事情。” 在RISC-V走向高复杂系统的时代,仅靠SoC厂商“自研调试链条”的方式已经难以为继。借助西门子EDA Tessent UltraSight-V这样“软硬结合、灵活扩展”的平台化调试解决方案,RISC-V SoC开发者将能大幅提升调试效率,加快产品迭代,真正缩短验证周期。

这不仅是解决Bug,更是重构系统可靠性的关键路径。