引言

在芯片设计的流片之路充满挑战,物理验证EDA工具无疑是这“最后一公里”关键且不可或缺的利器。它通过设计规则检查、版图与原理图一致性验证等关键流程,为IC设计契合制造需求提供坚实保障。作为签核(Signoff)环节的关键防线,物理验证EDA工具有力保障了流片的可靠性与成功率,堪称芯片成功流片的守护者。

在大规模数字/数模混合IC领域,随着芯片设计规模突破百亿晶体管级别,设计规则检查(DRC)的复杂度呈指数级增长,层次化并行验证加速成为提升DRC/LVS效率的关键。先进工艺的新型设计规则,如FinFET专属规则验证等,也要求物理验证工具不断创新。

在电源管理芯片(PMIC)领域,高压器件的可靠性检测至关重要。在存储芯片领域,海量阵列层次的处理与物理验证性能,直接影响芯片良率与成本。在射频(RF)芯片设计中,由于存在异形结构,如螺旋电感、传输线、复杂天线形状等,其物理验证往往难以通过普通EDA工具完成。

此外,随着Chiplet(芯粒)技术的兴起,先进封装(如2.5D/3D IC、异构集成)成为突破摩尔定律瓶颈的关键路径。为推动Chiplet大规模落地,实现跨工艺节点集成、多芯片电路与版图的一致性检查,高效物理规则验证成为关键技术挑战之一。

面对挑战,华大九天凭借30余年的深厚积累与深耕细作,成功打造了完整物理验证解决方案Empyrean Argus®,全面覆盖模拟、射频、存储、数字、面板等各类芯片设计与制造环节,并广泛适用于先进封装领域,提供Signoff级别的验证服务,为芯片产业的高质量发展提供了强大的技术支撑与保障。

Argus:以Signoff精度打造的全场景解决方案

物理验证平台Argus集成了多项核心物理验证功能,全面覆盖复杂设计场景。

1 设计规则检查 (DRC)

出色的通用DRC规则检查,涵盖距离、图形关系、密度、天线、电压等方面;可对版图进行逻辑运算等处理,并能针对图形、边及角度等各类数据开展高精度检查,并可对特定区域进行局部交互式检查。其DRC Flat模式创新性地引入多线程支持功能,显著提升了规则检查效率。

2 版图与原理图一致性检查 (LVS)

支持层次化版图网表高效提取,可自定义HCELL。提供特殊路径检查、短路/开路路径分析的ERC应用,具备灵活的器件提取语言,可精准提取后仿所需多种参数,适用于电源驱动芯片中的高压器件、图像传感CIS特殊结构及3DIC器件提取。针对超大规模SoC电路,Argus的LVS工具验证速度更快,性能优势显著。

3 版图与版图对比 (LVL)

支持多机并行,可对不同类型电路版图实施自适应预处理,提升性能;具备双窗口反标结果显示等功能,满足用户多样化需求。

4 可编程电气规则检查 (PERC)

能够对Netlist流程进行Topological检查,提供丰富的Python编程指令,支持基于Pattern模式检索,降低规则与引擎的无效交互,同时支持数据与命令双并行处理。

5 冗余图形填充 (Dummy Fill)

支持先进工艺,涵盖鳍片高度、宽度限制、密度梯度规则及多图案化掩膜拆分;支持多种形状Dummy填充,以及多图形、多层次、堆叠、伸缩填充;具备密度优化与颜色拆分功能,满足光刻要求,可压缩层次存储数据以优化处理效率。

6 图形查找与匹配 (Pattern Match)

提供精准匹配和模糊匹配多种模式,支持层次化并行查找和匹配,方便用户快速定位版图中的重复结构或潜在设计缺陷。

7 先进工艺掩膜拆分 (Multi Pattern)

支持先进工艺 Double-Pattern/Multi-Pattern掩膜拆分,提供多种拆分冲突的输出形式,可将版图图形拆分到多张掩膜版,借助多重曝光技术,满足高图形密度工艺设计及先进工艺晶圆制造要求。

8 物理规则开发平台 (DRStudio)

提供界面化Design Rule开发平台,展示逻辑图的图层派生关系,助力开发者理清思路;通过交互式反标功能,提高DRC/LVS Rule-Deck Debug效率,凭借可视化工具快速验证规则逻辑并精准定位错误。

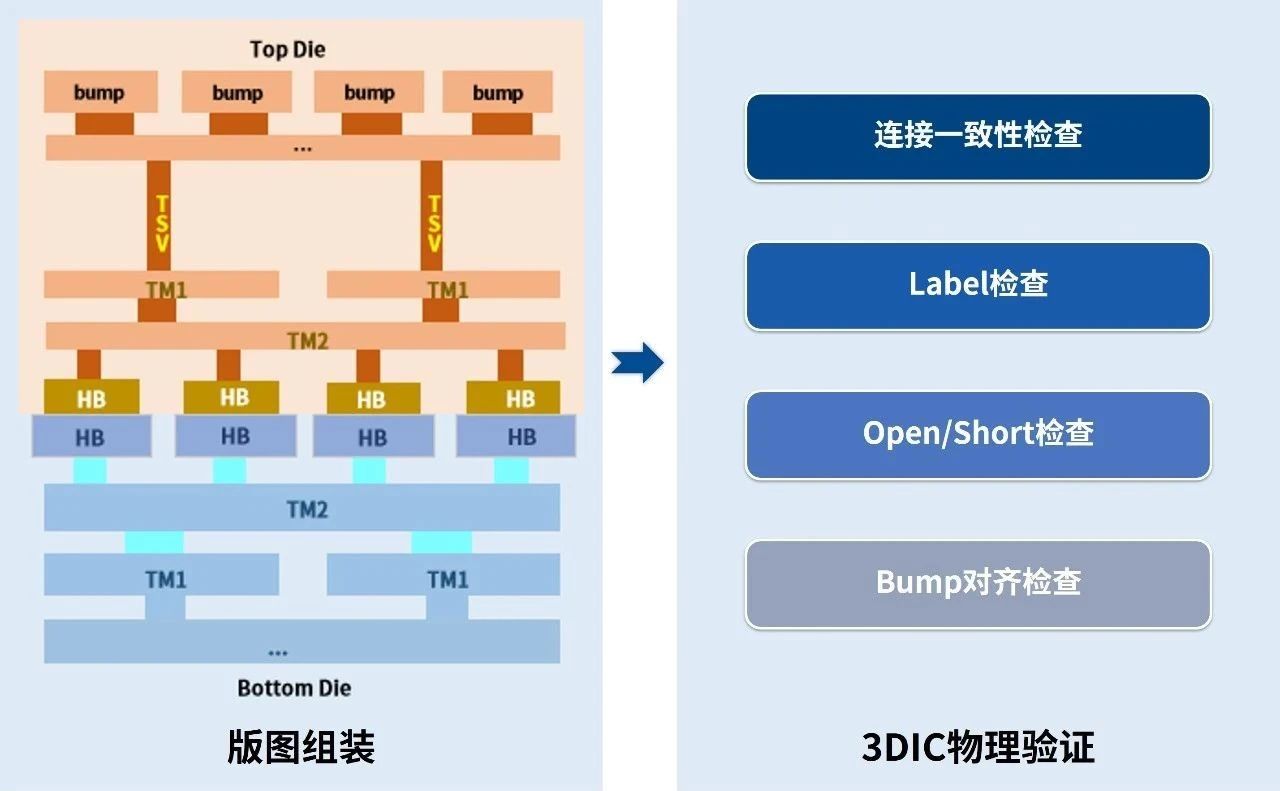

9 3DIC堆叠的跨工艺节点物理检查

针对复杂3DIC芯片堆叠场景,Argus可实现跨工艺多Die组装,自动解决版图冲突,并对3D系统界面进行一致性和连接性检查;支持用户自定义规则检查,支持Die在组装过程中进行放缩、旋转、翻转操作,更能开展千万级HB堆叠的高性能系统检查。

针对先进封装版图设计中因不规则图形导致的验证伪错及版图变形等难题,采用异形版图处理、容差处理、异构多芯片整合以及系统连接关系检查等核心技术,突破先进封装转接板中电源地信号开路的辨别难题,并深度耦合先进封装自动布线工具,实现版图设计期间根据局部区域和检查项目筛选进行快速设计规则检查,验证前移,大幅提升校错精度和效率。

技术突破:引领行业变革

Argus 在研发创新、技术应用和生态布局方面展现出高精度、高性能、高效率和易用性,形成全链条优势。它提供Signoff级别的物理验证高精度,无论异形结构还是复杂器件都能精准处理。其Flatten模式支持多线程并行处理,多机并行分布处理技术达到业界领先水平,CPU调用可超过1000核。

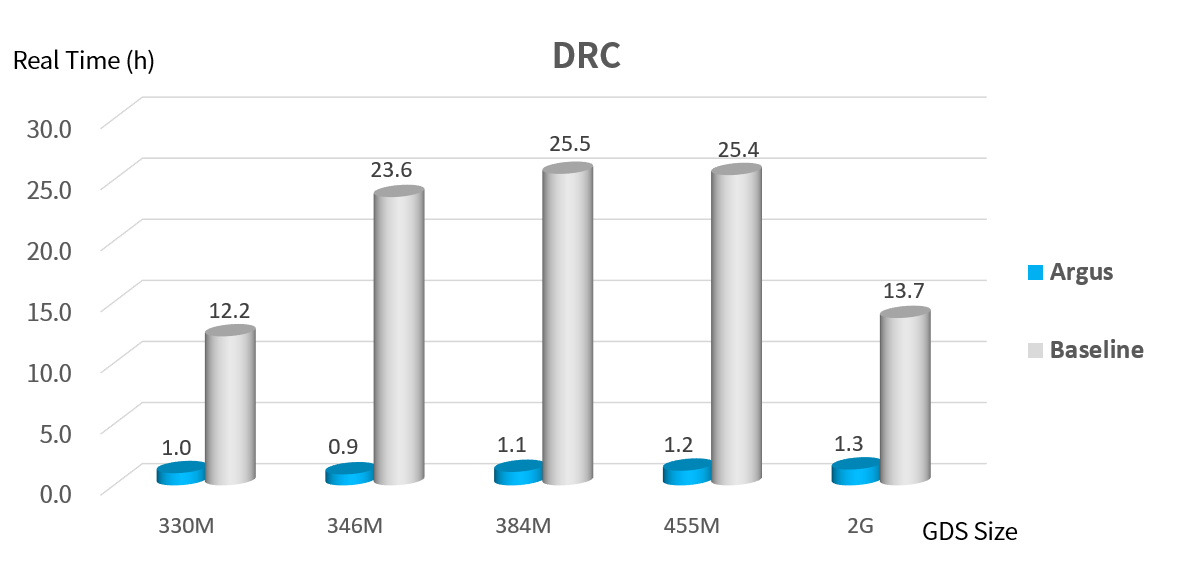

Argus的显著性能优势获得了客户的广泛好评。下图展示了不同GDS Size芯片在16核CPU测试条件下的DRC验证性能比较。不同芯片规模下,Baseline(灰色)耗时都远高于Argus(蓝色),Argus的加速比可达5-10倍。

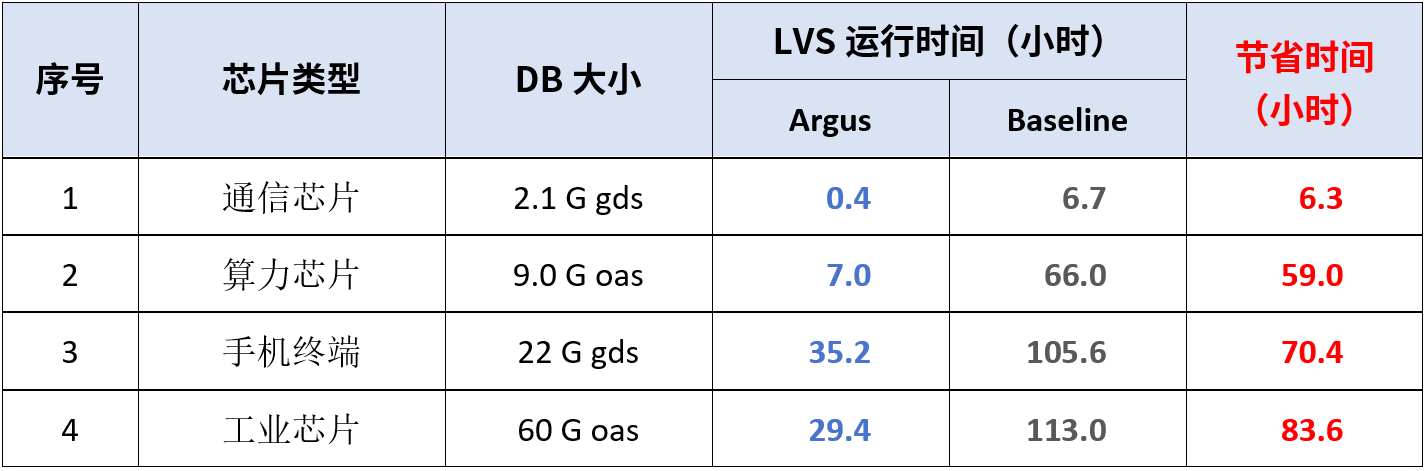

在超大规模SoC的LVS验证场景中,Argus的速度优势尤为突出。验证2G规模版图仅需0.4小时,对比Baseline的6.7小时,节省了半天时间;面对超大规模60G设计,Argus更是可以节省83.6小时,这相当于为整个研发团队争取了宝贵的3.5天,为芯片设计迭代带来了极为显著的加速效果。

在液晶面板领域,Argus不仅满足主流物理验证需求,还提供圆弧处理、伪错去重等特色解决方案,凭借这些优势,已占领中国超95%的市场份额,成为面板领域事实上的Signoff标准。在大规模数字及数模混合IC领域,由于版图数据量大、设计规则复杂,传统物理验证工具性能不足,成为设计迭代的瓶颈。Argus通过层次化与并行算法创新,实现了2-5倍以上性能提升,在市场竞争中取得了显著的技术优势。在泛模拟设计领域,Argus在电源管理芯片的高压可靠性检查覆盖率、存储芯片阵列层次处理与验证性能以及射频定制规则等方面持续创新,助力数百亿颗芯片成功量产。在先进封装领域,随着3D堆叠与Chiplet技术的兴起,华大九天与先进封装厂紧密合作,开发出多芯片版图集成验证解决方案,引领市场发展。在晶圆制造领域,Argus已经通过三星、XFab等知名海外厂商的认证,国内几乎所有晶圆制造厂都在与华大九天展开合作,加速设计工具和规则的迁移与应用。

结语

作为一款全面支持先进工艺、并获得ISO26262国际车规安全标准认证的新一代物理验证平台,Argus已在超过100家客户的实际项目中得到广泛应用和验证。从消费类电子到工业级芯片,再到汽车电子,高性能计算等领域,华大九天的物理验证产品线在功能对标齐全的前提下,已经从技术及应用层面展现出超越之势。凭借更多晶圆制造厂及IC设计公司的支持,结合中国研发速度的优势,华大九天定将打破垄断,通过技术优势助力中国芯片产业的快速发展。

来源:华大九天