作者:电子创新网张国斌

提到RISC-V,大家脑海里一定闪过四个字“开源架构”! 网上随便一搜,到处都是“RISC-V 是开源指令集架构”的表述。

但是,这个表述是错误的!错误的!错误的!

因为在RISC-V基金会官网上,关于RISC-V的表述是“to define RISC-V open specifications”而非“open code”,在这段文字下面,也写了“Understanding the RISC-V ISA Open Standard”,强调了RISC-V是一种“开放标准/规范”而非“开源架构”,为了搞清楚其中的缘由,我专门采访了中国RISC-V产业联盟理事长,上海开放处理器产业创新中心理事长,芯原股份创始人、董事长兼总裁戴伟民博士。

戴博士表示他确实注意到很多媒体包括一些专业机构都把RISC-V表述错了!

他指出RISC-V只是一种开放的“标准指令集架构”,应该称之为“开放指令集架构”,而不是“开源指令集架构”,而基于RISC-V指令集架构的产品实现(RISC-V的微架构、RISC-V的IP核或芯片),会产生“开源项目”、“企业自研”、“第三方商业IP”三种产品形态等,这些可以用开源或闭源来表述。

“基于开放标准实现的开源项目可以和非开源同类产品长期共存,各有优势,在竞争中取得各自的发展和平衡,比如你用RISC-V设计了一个处理器IP ,你可以将其开源也可以闭源。”他指出。

他进一步指出开放(Open)核心含义是标准可自由使用,无专利或授权限制,而开源(Open Source)核心含义是具体实现代码公开、允许修改/分发;开放适用对象是规范/标准(如RISC-V ISA文档),开源适用对象是实际代码/设计(如处理器RTL)等,在商业限制上,开放意味着可自由实现,无需付费或授权,开源则意味着需遵守开源协议。

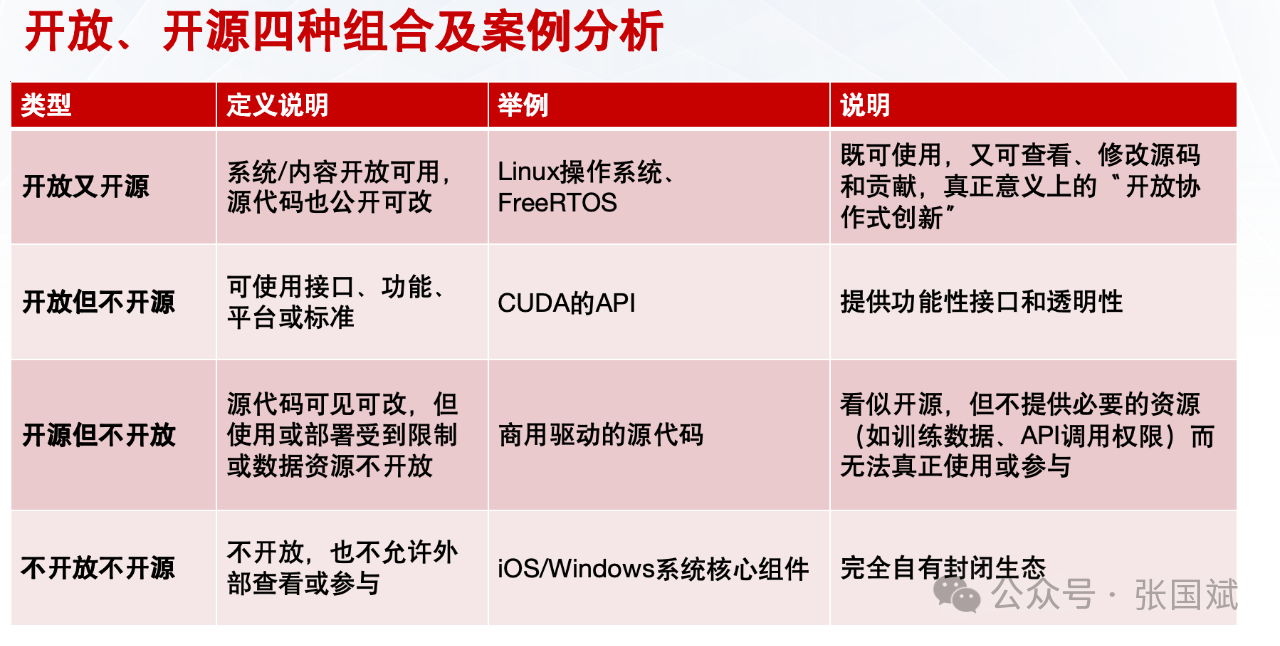

他举例说开放、开源四种组合分别是:

开放又开源: 系统/内容开放可用,源代码也公开可改,例子是Linux操作系统、FreeRTOS等,使用时候既可使用,又可查看、修改源码和贡献,真正意义上的“开放协作式创新”。

开放但不开源: 可使用接口、功能、平台或标准,典型例子是英伟达 CUDA的API ,它提供功能性接口和透明性。

开源但不开放:源代码可见可改,但使用或部署受到限制或数据资源不开放,典型例子是商用驱动的源代码,其看似开源,但不提供必要的资源(如训练数据、API调用权限)而无法真正使用或参与。

不开放不开源: 不开放也不允许外部查看或参与,典型例子是 iOS/Windows系统核心组件,它是完全自有封闭生态。

从指令集上如何理解开源开放?

那从指令集上如何理解开源和开放呢?他解释说指令集架构(ISA, Instruction Set Architecture)是处理器提供给软件(操作系统、编译器、应用程序)的抽象接口,规定了支持的指令集(如加法、跳转、加载/存储等指令)、寄存器数量和功能(如通用寄存器、程序计数器、状态寄存器)、内存访问模型(如地址空间、对齐要求、异常/中断处理机制(如系统调用、硬件中断))等。

“指令集ISA并没有规定CPU的设计以及实现,CPU的设计是通过微架构来定义的,指令集架构只适用'开放'和'不开放'的概念,不适用'开源'的概念。”他指出,“而微架构是ISA的硬件实现方式,决定了处理器内部的流水线设计(如几级流水线、乱序执行)、缓存结构(L1/L2/L3 缓存大小、关联性)、分支预测策略(静态预测 or 动态预测)、并行计算单元(如超标量、SIMD 单元)等,微架构由CPU架构师定义,并由CPU设计师完成,决定了一个CPU的性能,微架构实现只适用 '开源'和'不开源'的概念,不适用'开放'的概念。”

ISA 和 微架构的区别对比:

项目 | 指令集架构(ISA) | 微架构(Microarchitecture) |

|---|---|---|

本质 | 规范(“说什么”) | 实现方式(“怎么做”) |

面向 | 软件层 | 硬件工程 |

稳定性 | 稳定,变化小 | 可高度优化、变化大 |

示例 | RISC-V、x86、ARM | Rocket、BOOM、SiFive E76、Intel Skylake |

兼容性 | 不同微架构共享同一个ISA,程序可以运行 | 不同微架构实现效率不同,但功能一致 |

戴博士指出半导体历史上诞生过很多的指令集架构,最著名的有x86 - CISC、ARM - RISC、Power 、MIPS等等。

由此,我们可以对RISC-V的几个基本概念理解为:

RISC-V指令集(Instruction Set)仅描述指令的语法和功能;RISC-V指令集架构(ISA)定义指令集 + 寄存器、内存、特权模式等完整规范;RISC-V微架构定义了单个CPU核心的内部实现,包括流水线、缓存、分支预测、乱序执行等;RISC-V IP 核则是基于RISC-V的可商用处理器模块。

进而对CPU的开放开源才有了这样的表述:

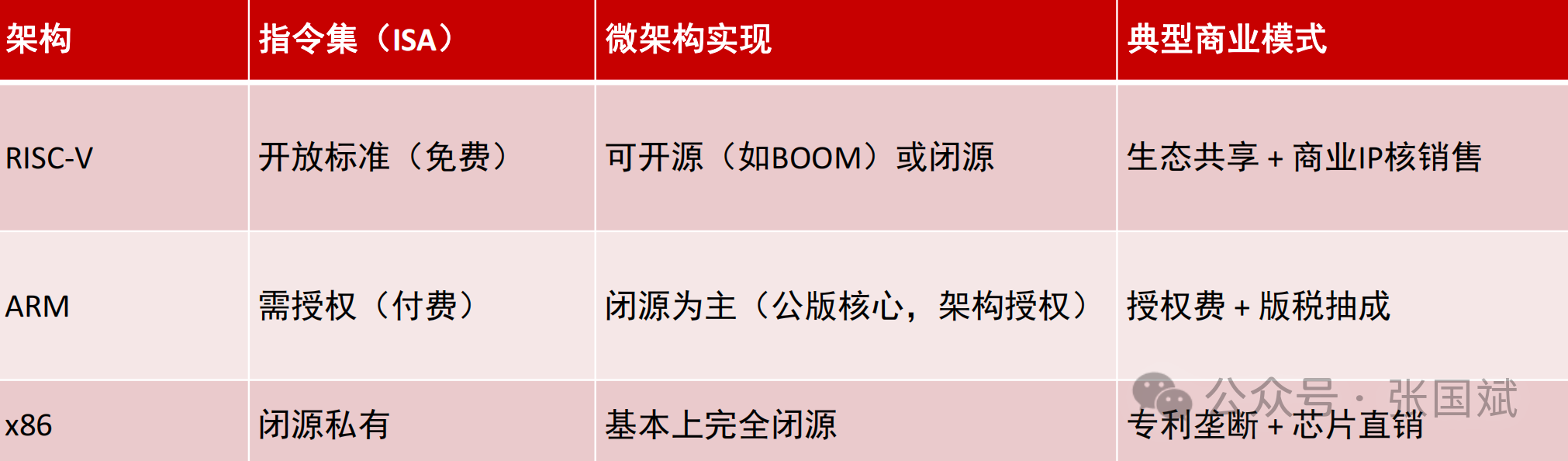

RISC-V的指令集是开放标准(是免费的),其微架构实现可开源(如BOOM)或闭源,其典型商业模式是生态共享+商业IP核销售。而ARM的子指令集是需要授权(付费),其架构实现是闭源为主(公版核心,架构授权),其典型商业模式是授权费+版税抽成,x86的指令集则原则上闭源私有的,其微架构实现基本完全闭源,其典型商业模式是专利垄断+芯片直销!

在RISC-V刚刚兴起时曾经也有人疑惑,这样的标准和ARM区别在哪里?哪里是开源的?经过这样的对比,相信大家都清楚了。

古人云:“名不正则言不顺,言不顺则事不成”,RISC-V作为一种开放指令集标准,不仅为全球半导体产业提供了打破垄断、降低成本、加速创新历史机遇,也在中国半导体产业展现了一条CPU安全、可控、繁荣和创新的发展之路,特别是在物联网、汽车电子和AI等领域。

目前中国已经构建了完整的RISC-V生态链,涵盖IP核、EDA工具、芯片设计、制造和应用等环节,预计到2030年,中国RISC-V芯片市场规模将达到250亿美元,年复合增长率高达47.9%!

在此关键节点,RISC-V更需要正本清源,以扫除障碍,获得强大的发展动力!

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利