作者:电子创新网张国斌

昨天有读者后台问了一个问题:为什么手机基带设计那么难?苹果挖了很多人搞了那多年都没彻底解决?这里从设计挑战、内部架构以及整体支出角度给大家科普一下。

手机蜂窝基带(Cellular Baseband)是手机通信系统的“大脑之一”,负责实现从物理层到中高层协议的数据处理、控制与调度,其功能相当于把射频收发回来的模拟信号变成手机能用的数据,或者反过来将上层的数据封装、编码成可发射的无线信号。

一、基带的基本功能

蜂窝基带主要处理以下功能模块:

功能模块 | 说明 |

|---|---|

物理层(Layer 1)处理 | 包括调制解调、信道编解码、信道估计、MIMO处理等,是整个通信数据路径的底层核心 |

媒体访问控制(MAC)层 | 负责资源调度、数据分段重组、重传机制(HARQ)等 |

RLC/PDCP/RRC等协议处理 | 管理数据加密、完整性保护、分段重组、连接控制等功能 |

功控/速率控制/时序控制 | 实现功率调节、调度命令处理、时间对齐(尤其TDD模式) |

多模制式切换与互操作性 | 支持2G/3G/4G/5G,甚至WLAN等多协议共存、切换 |

接口管理 | 包括与射频(RF)模块的数据通信,与应用处理器(AP)的高速数据通道(PCIe、SDIO、USB等) |

二、基带芯片的主要组成结构

基带芯片一般是高度集成的SoC架构,主要包括以下几个子模块:

1. 数字信号处理器(DSP)/专用加速器

负责物理层高强度计算:

调制解调(QAM、SC-FDMA、OFDM)

LDPC/Polar 编解码

信道估计与均衡

FFT/IFFT 等算法处理

高端设计中使用多个DSP+NPU+硬件加速模块协同。

2. 协议处理单元(Protocol Stack Processor)

通常为通用MCU或异构CPU(Arm Cortex-R/A系列);

执行RLC、PDCP、RRC等中高层通信协议;

处理安全、加密、信令连接管理、无线资源控制等任务;

某些任务可由协处理器或专用加密单元加速(如IPSec、SNOW3G/AES)。

3. 调度与资源管理模块

MAC调度器,控制上行下行资源的动态分配;

管理传输队列、重传缓存、HARQ反馈。

4. 时钟与同步模块

精确控制通信时序,支持帧/子帧级同步;

支持TDD/FDD时隙切换控制。

5. 基带与射频接口

通过 MIPI DigRF 或自定义高速并口与 RF 芯片通信;

处理IQ数据、控制字、时钟同步信号;

支持射频频段切换、PA/LNA控制、校准反馈。

6. 与应用处理器接口

USB/PCIe/SDIO 通道传输上层数据;

IPC(进程间通信)传输控制信息;

可集成共享内存区域供数据高速搬移(DMA)。

7. 功耗管理与睡眠控制单元

支持多级低功耗模式(例如eDRX、PSM);

联动射频、应用处理器、调度器进行整机功耗管理;

管理wake-up、resume、sleep等状态。

三、蜂窝基带芯片的逻辑结构图(文字简图) [ 上层协议栈处理器 ]

| RRC / PDCP / RLC |

-----------------------

| MAC 调度器 |

-----------------------

| 物理层处理器(DSP) |

| - OFDM/SC-FDMA |

| - LDPC/Polar Code |

| - MIMO/信道估计 |

-----------------------

| 时钟/同步管理模块 |

-----------------------

| 射频接口 | <----> 射频收发芯片

-----------------------

| 应用接口(PCIe) | <----> AP/Modem Host

[ 上层协议栈处理器 ]

| RRC / PDCP / RLC |

-----------------------

| MAC 调度器 |

-----------------------

| 物理层处理器(DSP) |

| - OFDM/SC-FDMA |

| - LDPC/Polar Code |

| - MIMO/信道估计 |

-----------------------

| 时钟/同步管理模块 |

-----------------------

| 射频接口 | <----> 射频收发芯片

-----------------------

| 应用接口(PCIe) | <----> AP/Modem Host

四、手机基带发展趋势

趋势 | 说明 |

|---|---|

Modem+AP深度集成(SoC化) | 如高通Snapdragon,将基带和应用处理器集成,提升能效与面积效率 |

向异构计算迁移 | 引入AI加速、VLIW/NPU/FPGA等架构,加速信号处理与协议堆栈 |

支持多模多频高集成 | 包括5G NR、LTE、3G、2G、Wi-Fi、BT 的统一调度和互操作 |

软件定义无线电(SDR)能力增强 | 提高灵活性,降低未来制式演进成本 |

节能与动态功控更智能 | 节能是永恒课题,特别在IoT/智能穿戴/6G等低功耗场景下 |

五、手机基带设计难在哪里?

手机蜂窝基带(Cellular Baseband)设计堪称是现代SoC系统中最复杂、最高壁垒的部分之一,其挑战来自于技术难度极高、标准复杂、集成度高、验证周期长、专利门槛重重

以下是几个主要方面的设计挑战和难点:

5.1、协议复杂且不断演进

我们所处的通信是多代并存 ,目前是2G/3G/4G/5G乃至未来6G,这每一代通信协议涉及的信道结构、调制编码方式、链路控制机制都不同。基带需要同时兼容多种制式、支持多频段和载波聚合(Carrier Aggregation)这就增加了架构的复杂性。

以3GPP标准为例,每一版Release有数千页技术规范。标准更新频繁,设计需灵活适配,标准跟随能力是技术壁垒之一,要紧跟标准必须有大量技术人员参与其中。

5.2、实时高并发信号处理挑战

由于基带芯片负责整个通信链路的物理层(PHY)和部分MAC层处理, 因此超高性能要求,尤其在5G NR中,涉及大规模MIMO、多用户并发、低时延要求、上下行高吞吐量场景下,计算量和带宽压力非常大,常用 SIMD/VLIW/DSP/NPU 协同设计。

此外,实时性和确定性也让设计挑战非常大,例如 HARQ(Hybrid ARQ)反馈机制要求在几百微秒内完成计算、解码和响应,而任何延迟都可能引发数据重传,影响网络性能。

5.3、软硬件协同复杂

基带的硬件架构非常复杂、包括调制解调(Modem)、信道编解码(Turbo/LDPC/Polar Code)、信号估计、均衡、同步等模块。它高度依赖异构计算单元(DSP/NPU/ASIC块)协同。而同时,其软件栈也异常繁重:协议栈实现难度大,从L1(物理层)到L3(网络层)要与操作系统和应用协同。功能众多,协议兼容性、稳定性、可调试性要求高。

5.4、多频段支持和射频协同

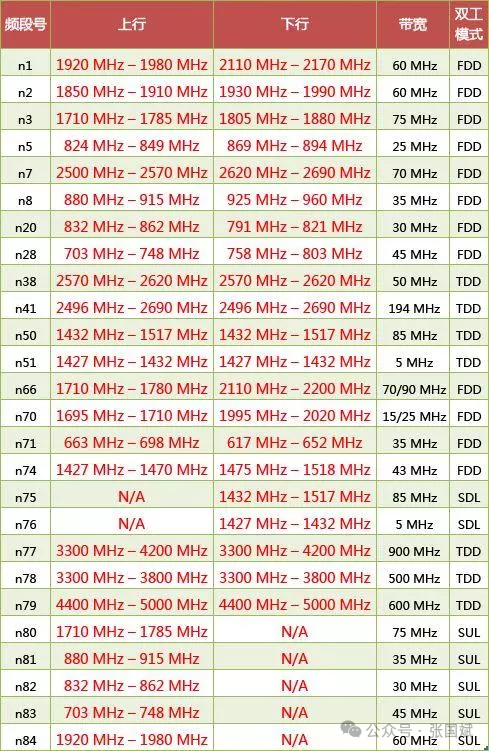

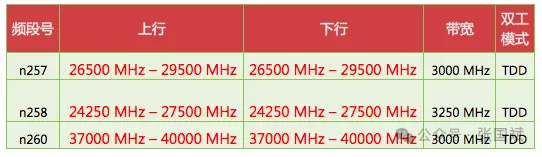

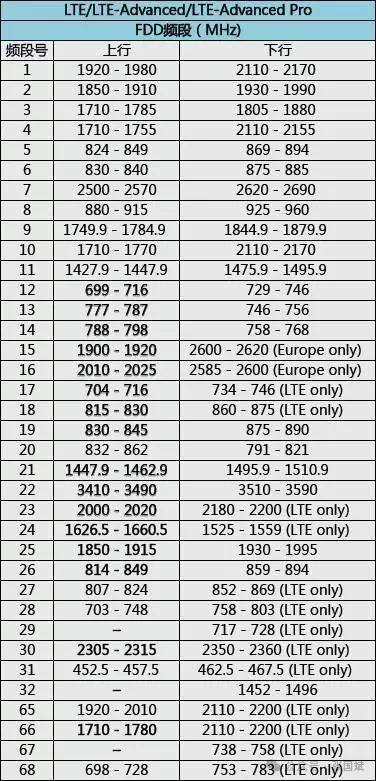

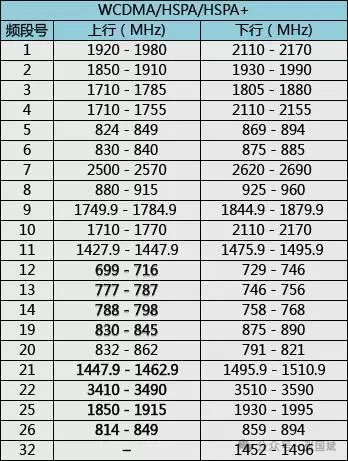

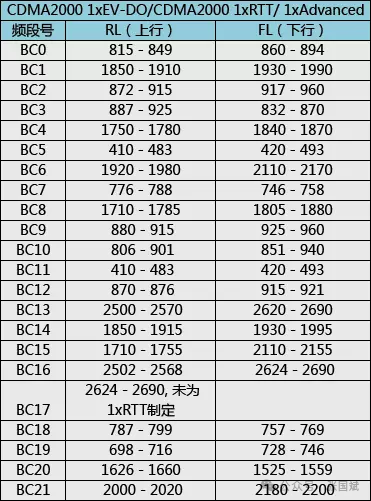

蜂窝通信要支持全球网络,基带就要获得和处理不同国家通信频带的信号,虽然基带本身不处理模拟射频,但频段、调制方式和射频前端必须高度匹配,支持全球运营商网络需适配数十种频段(尤其5G Sub-6 + mmWave)。射频前端和基带之间需要高效的数字接口(如MIPI DigRF)。基带设计必须考虑频谱利用效率、功耗动态调整等与射频的协同优化问题。这里我在网上找了一些资料把目前2G3G4G5G的频谱频带划分展示一下:

目前3GPP已指定的5G NR频段具体如下:FR1 (450 MHz–6000MHz):

FR2:

4G LTE频带

3G WCDMA

3G TD-SCDMA

TD-SCDMA

频段号频率范围(MHz)

331900 - 1920

342010 - 2025

351850 - 1910

361930 - 1990

371910 - 1930

382570 - 2620

391880 - 1920

402300 - 2400

2G GSM

备注:

P-GSM,基准GSM-900频带

E-GSM,扩展GSM-900频带(包括基准GSM-900频带)

R-GSM,铁路GSM-900频带(包括基准和扩展GSM-900频带)

T-GSM,集群无线系统-GSM

ER-GSM900,即为Extended Railway GSM 900, 在原铁路通信系统的基础拓宽了其频率范围(TX:873-915,RX:918-960)。

CDMA

要适配如此多的频段,设计挑战可想而知!

5.5、极致功耗控制

手机设备对功耗极其敏感,基带芯片需支持多级动态功耗管理(DVFS、时钟门控、睡眠唤醒机制),5G下行速度提升意味着芯片内部数据搬移量极大,需优化DMA、总线和缓存系统以控制功耗。

5.6、验证与测试极其复杂

覆盖所有协议场景、频段、网络拓扑的测试极其耗时,常用百万条用例。还需进行现场网络验证(field test),涉及不同国家、运营商和设备厂商。许多bug仅在极端网络环境下复现,验证周期可长达1-2年,这个挑战也是非常巨大的,不但需要人力物力还需要去当地测试,不过 一些测试可以委托给运营商。

5.7、知识产权和专利壁垒

在移动通信领域,华为、高通、爱立信、诺基亚、三星等持有大量相关基础专利,要设计基带无法绕开很多专利,避开专利雷区并确保协议兼容,是新进入者面临的巨大法律和技术挑战

总结下来基带设计挑战主要体现在

因素 | 描述 |

|---|---|

技术复杂度 | 多协议、多频段、异构计算、实时处理 |

标准壁垒 | 需精通3GPP协议,标准演进快 |

系统集成度 | 与射频、天线、AP协同,SoC封装难度高 |

功耗要求 | 多模式动态控制、热设计挑战大 |

验证难度 | 长周期、多场景测试,不容出错 |

专利门槛 | 极高的IP壁垒和授权成本 |

举个例子,看看5G基带中的 LDPC 解码加速设计

LDPC 是 5G eMBB 场景的主力信道编码,5G 新空口(NR)在物理层上使用了两种信道编码方案:

LDPC(Low-Density Parity-Check):用于下行与上行共享信道(PDSCH/PUSCH)的大部分数据传输。

Polar Code:用于控制信道(如PDCCH)。

LDPC 相比 Turbo 编码(4G主力)在并行性、误码率性能、低时延方面更适合大数据量高速传输。

✦ LDPC 解码的挑战:

迭代运算密集:

LDPC 是一种基于图的迭代解码算法,最常用的是 Belief Propagation 或其近似(Min-Sum)。

每轮迭代涉及大量乘加、最大/最小值运算,计算密集度高。

吞吐量要求高:

下行用户速率可达 Gbps,LDPC 解码必须在数百微秒内完成。

硬件并行性设计复杂:

LDPC 的码本结构稀疏,但具有行列关联性,需专门设计交织器(interleaver)、调度机制避免数据冲突。

✦ 加速设计手段:

技术点 | 描述 |

|---|---|

并行解码架构(Parallel Decoder Array) | 通过构建多个并行处理单元(PE),分摊行列节点处理任务 |

Min-Sum Approximation | 用于近似简化Belief Propagation中的复杂函数计算 |

内存访问优化 | 通过专用交织存储器设计(RAM Bank)减少冲突和等待 |

动态迭代控制 | 支持早停机制(early termination),节省功耗与延迟 |

可配置LDPC内核 | 提供灵活可配置结构支持不同码率、码长 |

有些高端芯片会为 LDPC 解码单独设计 ASIC IP(如高通X70),而国产玩家往往以 DSP+ASIC 混合架构起步。

射频(RF)与基带协同的接口设计

前面说过,在手机SoC中,基带负责数字信号处理,射频芯片负责模拟射频发射/接收。二者需要通过高速数字接口协同工作,关键接口包括:

IQ数据接口

控制与状态接口

同步时钟接口

✦ 射频-基带接口关键标准

接口标准 | 描述 |

|---|---|

MIPI DigRF v4/v5 | 支持最高10Gbps,主要用于基带与射频芯片之间的数据传输 |

JEDEC JESD207 | 用于收发数据与控制信息 |

SLVS/CMOS接口 | 低速控制路径,例如射频频段切换、校准 |

TSF(Timing Synchronization Function) | 保证时钟同步,满足TDD上/下行切换、MIMO同步精度 |

协同设计的难点

数据速率极高:

IQ样本速率高,尤其在载波聚合和多天线(MIMO)环境中。

要求接口具备高带宽、低延迟、低抖动(jitter)特性。

射频功耗动态调节与基带联动:

例如在信号弱时动态提升PA(功率放大器)增益,在空闲时关闭LNA。

这些调节动作需由基带实时控制,确保网络稳定。

多通道MIMO同步要求严苛:

上下行信号必须精确同步,涉及多个通道的相位对齐、时钟校准。

校准机制与闭环反馈:

包括射频校准(IQ平衡、DC offset)与发射功率控制(TPC)。

基带需实时反馈并更新RF参数,形成闭环控制。

✦ 典型实现方式(简化图示)| 基带芯片 |

|----------|

| 数字基带处理器(DSP) |

| LDPC解码模块 |

| 调制/解调模块 |

| 数模转换(DAC) |

| MIPI DigRF 接口 ---------> 射频芯片

| 射频前端(LNA/PA/Filter)

| 频率合成器

| 模数转换(ADC)

| 射频开关控制器

| 基带芯片 |

|----------|

| 数字基带处理器(DSP) |

| LDPC解码模块 |

| 调制/解调模块 |

| 数模转换(DAC) |

| MIPI DigRF 接口 ---------> 射频芯片

| 射频前端(LNA/PA/Filter)

| 频率合成器

| 模数转换(ADC)

| 射频开关控制器

总结对比

模块 | 设计重点 | 挑战 |

|---|---|---|

LDPC 解码 | 高吞吐、并行计算、低功耗 | 解码算法复杂、功耗/延迟限制、架构优化困难 |

射频协同接口 | 高频率IQ数据传输、同步控制、射频调节 | 接口带宽、射频行为控制、跨域同步 |

设计一款兼容多模(2G/3G/4G/5G)蜂窝基带芯片,是当前半导体行业中最复杂、最烧钱、门槛最高的项目之一。这类芯片不仅仅是设计电路,更需要对通信标准、算法、系统验证、射频协同、软件协议栈、认证测试、IP授权、量产流程等全流程进行重度投入。

以下对人力、资金、周期等核心投入的系统性评估(这是某AI大模型给出的总结,仅供参考):

一、资金投入估算(基于中高端5G多模基带)

阶段 | 内容 | 预估成本(人民币) |

|---|---|---|

❶ 前期IP授权/标准许可 | 购买LDPC/Polar Code IP、3GPP协议库、高速接口IP(如PCIe、USB、DDR)、Arm/DSP授权、标准专利池费用(如MPEG LA、Sisvel、ETSI) | 1~2亿元 |

❷ 芯片设计与验证 | 架构设计、RTL开发、FPGA原型验证、前后端设计、低功耗优化、DFT/DFD等 | 3~5亿元 |

❸ 芯片流片 | 多次工程流片(28nm/16nm/7nm),每次费用3000万1亿不等,考虑35次迭代 | 1~3亿元 |

❹ 软件栈开发 | 包括物理层算法固化、中高层协议栈(RRC、MAC、RLC、PDCP)、调度器、功耗控制、通信协议适配(Android/Linux) | 1~2亿元 |

❺ 验证测试与认证 | 实验室测试、射频一致性测试、全球各国/各运营商认证(GCF/PTCRB/CE/FCC/运营商定制测试) | 5000万~1亿元 |

❻ 工具/测试平台购买 | 原型验证FPGA平台、协议分析仪、通信测试仪(如Keysight、R&S 5G仪表),搭建真实网络环境 | 数千万元 |

总计 | 12亿 |

注:以上是有经验团队且已有基础IP积累情况下的合理估算。初创团队从零起步,则投入可能更高,时间更长。

二、人力投入需求

角色类型 | 细分岗位 | 人员规模(估算) |

|---|---|---|

系统/算法 | 通信系统架构、MIMO/调制算法、LDPC/Polar设计、同步时钟设计 | 50~80人 |

前端设计 | RTL设计、功耗优化、接口逻辑(AXI/AHB等)、内存控制器、SoC总线 | 50~70人 |

后端设计 | 综合、布局布线、时序收敛、DFT/DFD、EM/IR分析 | 30~50人 |

软件团队 | 物理层固件、MAC层调度、RRC协议、驱动栈(Linux/Android)、功控管理 | 100~150人 |

验证/测试 | 仿真验证、FPGA验证、协议一致性测试、运营商场测、工信部测试 | 50~100人 |

系统集成与PM | 产品管理、跨部门协作、平台验证、IP集成、运营商对接 | 20~40人 |

其他 | 射频协同、UI交互、客户支持、市场/售前等 | 20~30人 |

合计:300~500人左右的跨学科高水平团队,至少需持续投入2~3年。

三、周期预估

阶段 | 时间 |

|---|---|

架构设计与前期调研 | 3~6个月 |

设计开发阶段 | 12~18个月 |

初次流片与调试 | 6~9个月 |

验证与认证、量产准备 | 6~12个月 |

合计 | 2.5~3.5年 |

四、面临的关键风险

专利封锁:高通、爱立信、诺基亚等拥有大量SEPs(标准必要专利),需谨慎规避或支付许可费用;

协议兼容问题:3GPP兼容性测试要求极高,容易在小众场景或边缘情况出错;

量产难度大:工艺迁移、良率控制、封装测试、功耗控制等对团队经验依赖极高;

市场与资金回报周期长:在没有成熟运营商订单的情况下,ROI周期可能超5年;

竞争环境残酷:目前市面上成熟的基带供应商仅剩高通、联发科、三星、华为、紫光展锐等少数几家,已形成高壁垒垄断。

总结

设计一款兼容2G~5G多模蜂窝基带芯片:

维度 | 典型规模 |

|---|---|

人力投入 | 300~500人(覆盖硬件、算法、软件、系统) |

资金需求 | 8~15亿元人民币 |

研发周期 | 约2.5~3.5年 |

风险等级 | 极高(标准壁垒+专利+复杂度+验证难) |

总之,设计手机基带芯片挑战极大,风险极大,而且需要长时间的积累!该领域慎入慎入慎入!

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利