作者:电子创新网张国斌

2nm、GAA、3D封装、chiplet、异构....近年来,随着半导体工艺的进步,单颗IC的晶体管数量已经从百亿向千亿甚至万亿数量发展,功能复杂需求也让单颗IC也集成了越来越多的IP,此外 ,工艺的进步也带来了制造商良率的问题,这都给IC设计师带来了极大的挑战,一方面要应付工艺、复杂度提升带来的设计难度挑战,另外还要应付time-to-market带来的效率压力。

而熟悉IC设计的人都知道,过去十年中,IC设计中仿真验证成本的增长速度远高于设计成本。数据表明,包括工程师、软件、硬件在内的验证资源占到整个前端设计的70%,而设计本身只占30%,所以仿真验证在整个集成电路行业当中的占比会越来越高,而且随着工艺的升级,所占比还在提升(如上图所示),所以要确保芯片高效开发,就要提升仿真验证的效率。

5月31日,在电子创新网旗下芯英雄联盟直播频道举办的《EDA仿真最新趋势和效率提升》线上直播活动中,华为数据存储半导体行业解决方案架构师施钻专和概伦电子研发副总裁方君分享了提升EDA仿真效率一些做法。

1、华为存储四大举措提升EDA仿真效率

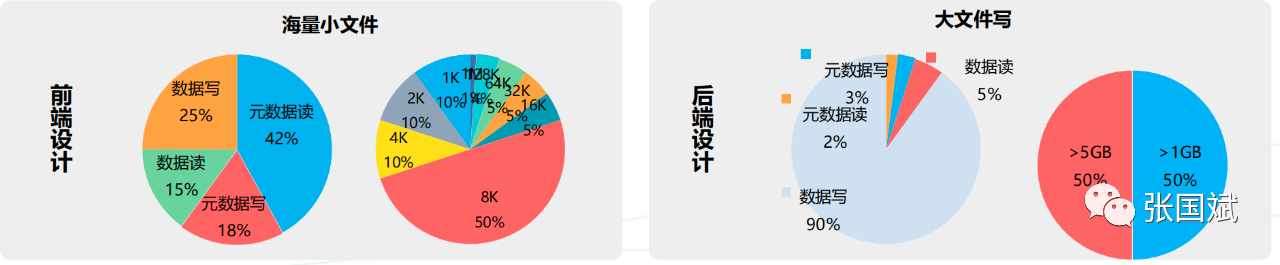

施钻专指出,目前,EDA仿真平台面临几个困境,一个是面对混合型业务,存储更容易成为瓶颈。这是因为EDA仿真主要分前端业务和后端业务。前端业务主要以RTL编码仿真为主,数据特点基本都是KB级别的小文件,并且主要是8KB左右的文件为主,超过60%以上都是元数据读写,这类场景针对存储的要求就是更高的OPS性能诉求。后端业务,主要以综合优化仿真、编译网表及网表测试为主,主要是GB级别的大文件写场景,这类场景对存储性能要求带宽更高。

EDA仿真平台面临的另个困境是解决方案不匹配或者不会用,表现在:

1、服务器本地盘方案资源利用率低投资浪费, 表现为项目组间资源无法调度无法共享;Temp文件增长迅速服务器容量受限容易爆盘;无专业存储企业特性,易用性差;数据安全无法保障等。

2、共享存储方案选型不对、导致仿真性能差影响研发进度。主要表现为分布式文件系统分片机制只适合大文件大带宽场景、 万亿海量KB级小文件性能不足,存储时延高,仿真卡顿、Lustre等文件系统需MDS等额外元数据节点服务器,增加故障点、高负载下删除时,EDA软件卡顿等。

3、专业存储不会规划使用,具体表现为不懂如何确保仿真业务不中断、关键仿真任务高效执行、不懂如何确保高价值数据安全性?不懂如何实现业务安全隔离、不懂如何在有限的存储空间实现价值最大化,这样会导致资源利用率低、投资浪费等。

针对这样的痛点,华为存储是如何提升EDA仿真效率的呢?施钻专表示华为存储联合IC设计企业在EDA设计仿真过程中的业务诉求,通过系列化的优化,打造半导体设计EDA存储解决方案,大幅缩短EDA仿真周期。

概括起来,有四大举措:

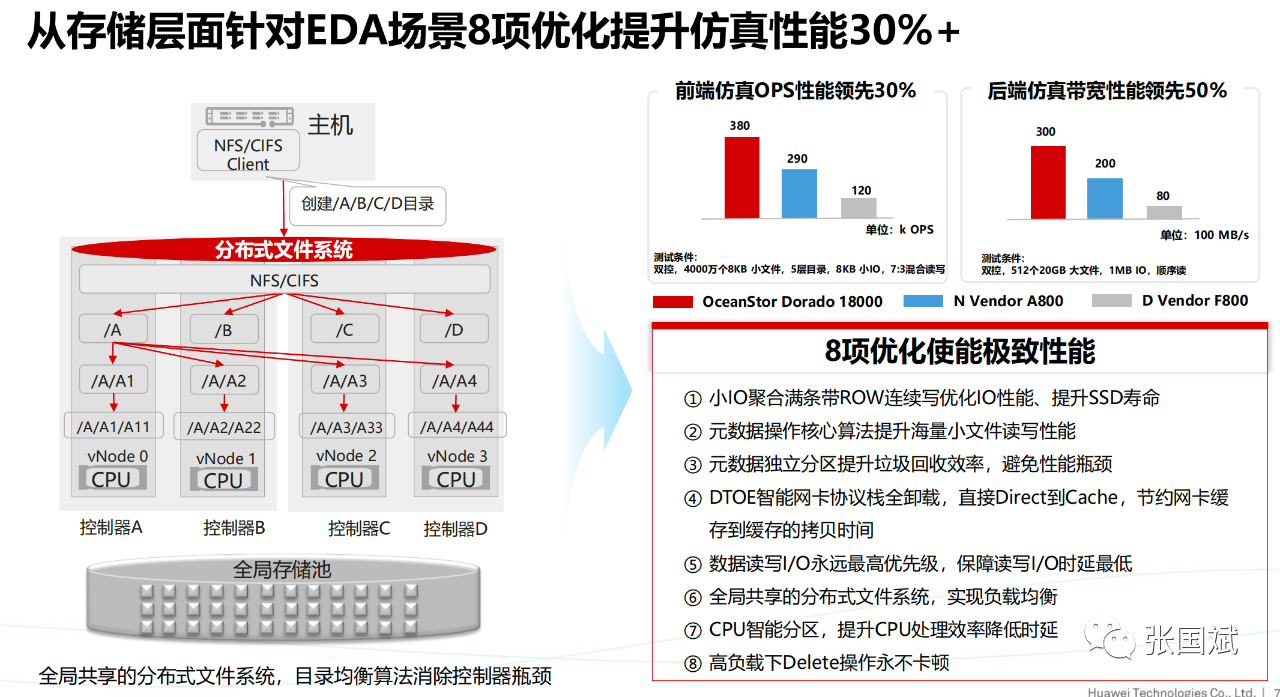

1、从存储层面针对EDA场景8项优化提升仿真性能30%+

施钻专表示针对海量小文件场景,可以通过小IO聚合满条带ROW连续写来优化IO性能,同时也提升了SSD寿命。

针对大量的元数据操作,通过多项核心算法,比如元数据的压紧算法,元数据的预取与淘汰算法等,提升元数据操作性能。

元数据和数据独立分区,有利于提升垃圾回收效率,消除性能瓶颈。

在硬件方面,华为存储专门用了DTOE的智能网卡,把协议从CPU卸载到网卡上,节约网卡缓存到缓存的拷贝时间。

CPU需要处理读写IO、GC、快照等其他特性,把读写IO优先级排最高,这样可以保障读写IO的时延最低。

华为存储采用全局共享的分布式文件系统,基于目录均衡打散,消除控制器的瓶颈,支持自动迁移热点目录到空闲控制器上,实现自动负载均衡。

华为存储使用多核鲲鹏920 CPU,通过CPU智能分区,绑核处理,避免跨CPU核跨控开销,提升CPU的处理效率、降低时延。

EDA场景会有大量删除Temp文件的操作,华为存储专门针对删除操作做了CPU绑核处理,专核专用,确保高负载情况下Delete操作不卡顿。

2、全闪存介质升级,能效优化降低整体TCO

施钻专表示存储介质主要分HDD机械硬盘以及SSD全闪存硬盘。以前大多数IC设计企业,会选择采用1.2TB左右的HDD机械硬盘,通过好几个硬盘柜来堆存储性能,但是这样会导致机房空间、功耗大幅增高。目前越来越多的IC设计企业,尤其是一些先进制程的比如7nm、5nm芯片设计企业,为了性能需求会选择SSD全闪存存储。

从投入产出比看,SSD应用可以大大降低企业的运维成本,相比于传统存储需要配置几十个磁盘机柜、上万块HDD磁盘,SSD只需要几个机柜即可;SSD不仅在空间需求上优势明显,在能耗、运维成本上也非常突出:相对于HDD,在相同的容量下,SSD的电力能耗降低70%,空间占用节省50%。在存储系统中每更换1块SSD,带来的节能减排效果,相当于种了150棵树,以及3360个普通家庭熄灯一小时。

3、存储层丰富的企业软件特性,帮助IC设计企业更好的管理数据提升效率

华为存储提供了很多丰富的软件特性,帮助IC设计企业更好的管理数据,提升工作效率。如多租户特性可以用来确保数据安全隔离。

施钻专表示EDA仿真临时文件较多,如果不做及时删除,空间就会被快速消耗掉,影响到其他用户,这个问题可以通过设置配额的方式来解决,确保存储空间的有效利用。有些关键仿真为了不被其他任务挤占掉存储性能资源,会特别设置一个关键VIP任务的最低性能要求,来确保仿真任务高效完成。

海量小文件一直都是EDA仿真场景的最大难题,华为存储不是通过备份软件对应用层扫描的方式来备份,而是通过底层的快照技术和异步复制技术,来做到Disk to Disk的快速备份,可以有效提升几倍甚至十倍的性能提升。

4、存储层四级可靠为EDA仿真平台平稳运行保驾护航

永远在线的方案:通过业界唯一的NAS Active-Active双活解决方案,确保单套存储故障时不会影响生产。

永远在线的系统:通过RAID TP可以容忍3块硬盘同时失效,另外全闪存储重构1TB时间只需要15分钟,解决块硬盘不影响生产的问题。

永远在线的架构:通过Smart Matrix全互联架构和独有的SMB Failover功能,可以容忍单套存储系统内单个引擎故障或者7个控制器故障,业务不中断。

永远在线的SSD:通过全局磨损与反磨损,来提升SSD的使用寿命,降低IT运维人员压力。

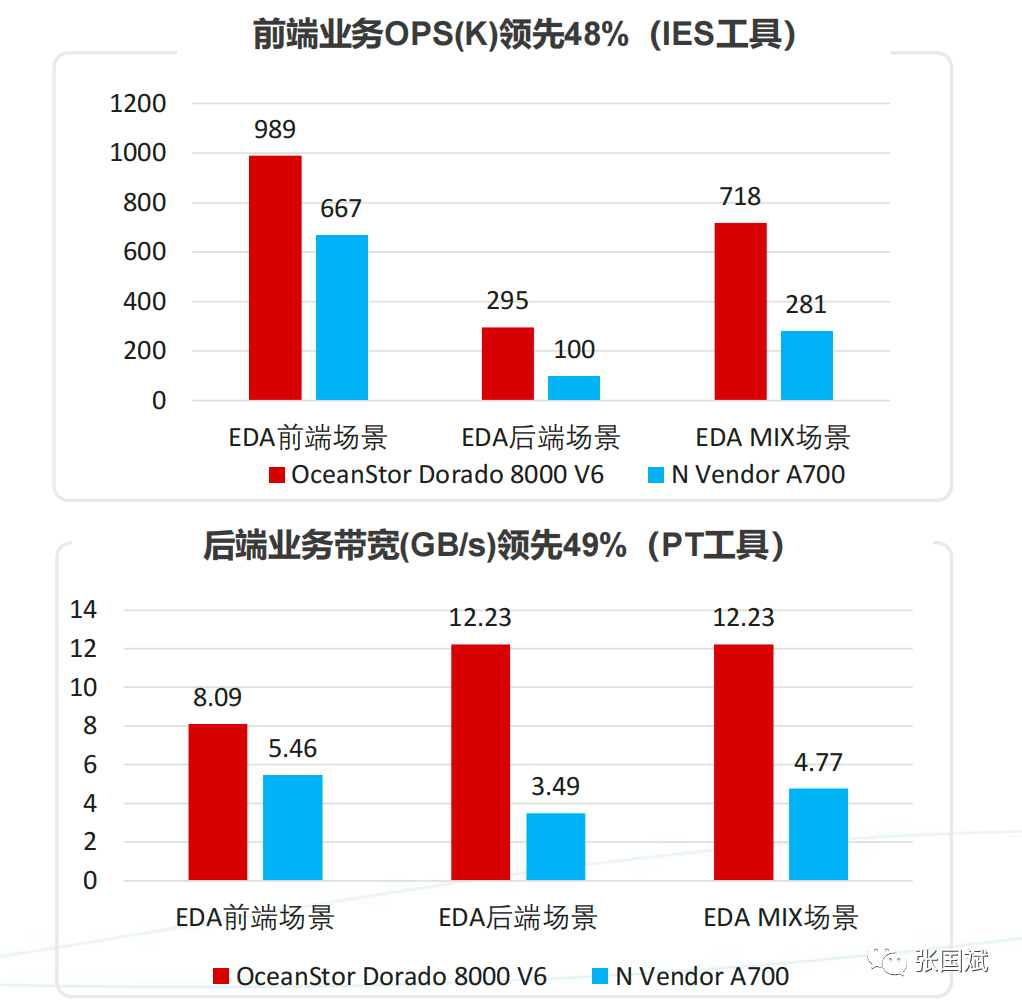

施钻专特别指出华为存储在海思EDA仿真平台使用表明使用之后其前端业务OPS领先48% ,后端业务带宽领先49%!

2、概伦电子如何提升EDA仿真效率?

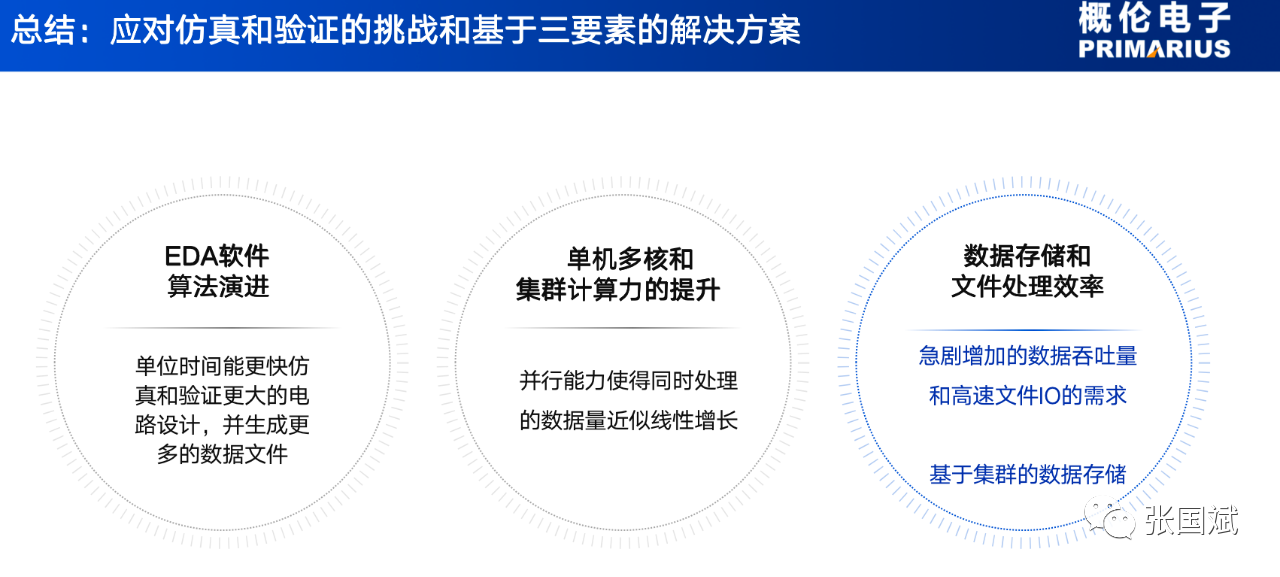

方君认为可以通过三个方面提升EDA仿真效率,分别是文件存储、EDA算法和算力资源。

文件存储体现在读写速度的不断提升以便处理超大文件、高性能文件IO以支持大量文件同时操作以及文件存储空间的扩展以满足数据量的不断增加。

EDA算法层面体现在EDA 仿真和验证工具的不断演进、更有效的数学算法,比如矩阵求解、更智能的电路结构检测和分区技术、更好硬件结合,高效的CPU指令集、存储管理等;

算力资源体现在多核服务器的支持、计算机集群的支持和速度优化、有效的任务分发和管理机制等。

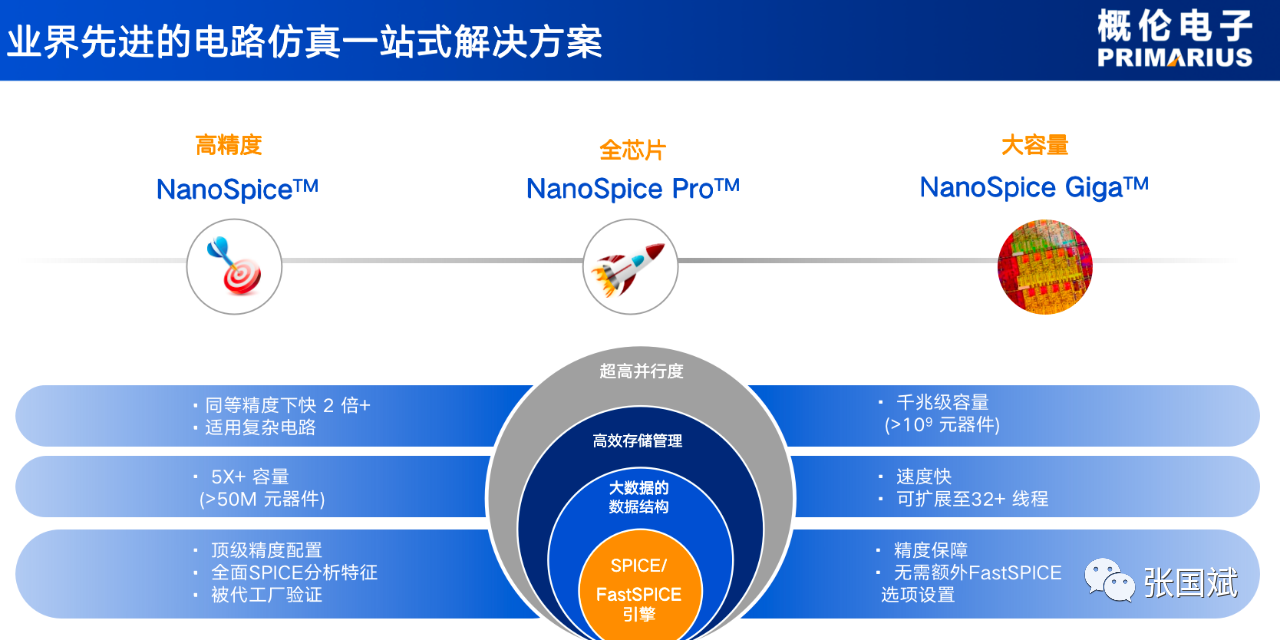

他指出概伦电子提供的是融合上述三个要素的一站式仿真解决方案,从仿真工具到标准单元库再到电路设计都有覆盖。

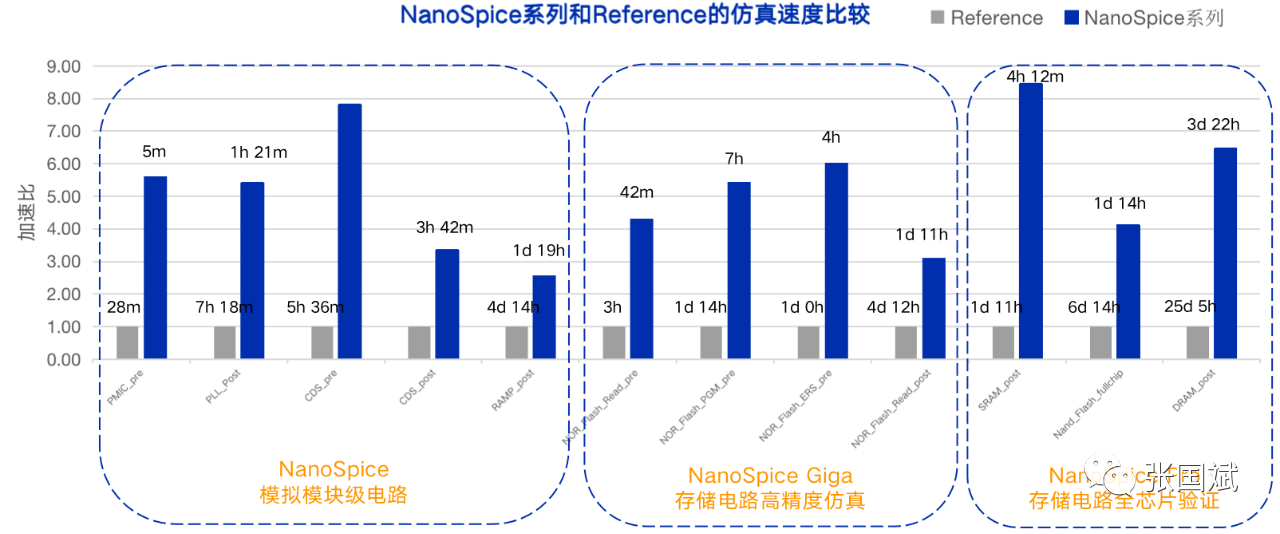

如NanoSpice就是概伦电子推出的新一代大容量、高精度、高性能并行SPICE电路仿真器,覆盖模块级模拟电路到全芯片存储器电路,特别对高精度模拟电路和大规模后仿电路的电路仿真进行优化,同时满足高精度、大容量和高性能的高端电路仿真需求。

NanoSpice Pro是一款概伦电子自主研发的FastSPICE电路仿真器,可满足存储器单元设计、存储阵列和编译器验证、存储器特征化及全芯片验证等所有需求,相比其它同类仿真器性能有较明显提高。

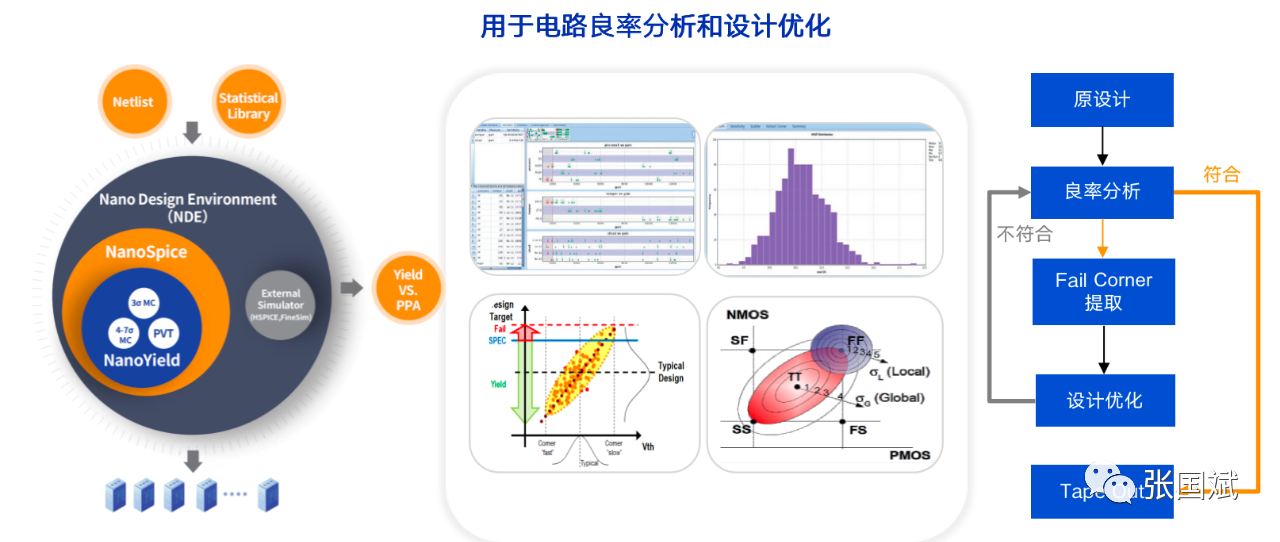

而概伦电子的NanoYield良率导向设计平台则可以用于电路良率分析和设计优化。

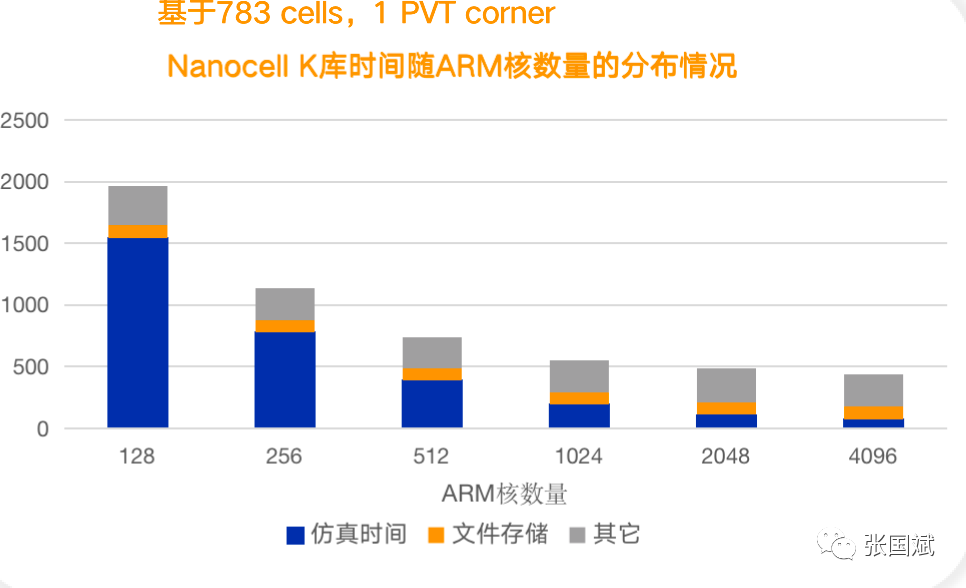

方君表示概伦电子的NanoCell 是一款快速精确且易用的标准单元库特征化 EDA 工 具,它通过内置的 NanoSpice仿真器,采用先进的分布式并行架构技术和单元电路分析提取算法,精确且高效的对单元电路进行时序、功耗及噪声等特征进行仿真与提取,提供友好易使用的接口,帮助用户缩短产品开发周期。它支持ARM/X86 环境。

此外他还强调,概伦电子建设有基于ARM架构的计算服务中心,服务器超过800台,CPU超过10万核,内存达800TB;服务器本地存储为10PB、 集中高速存储:270TB,网络方面支持25G网络互连 ,最大100G带宽 、支持全链路负载均负载。

他强调概伦电子会围绕三大要素持续和改进以提升EDA仿真效率。

半导体工艺会不断演进,未来EDA工具的重要性日益凸显,随着人工智能、大数据的应用深入 ,EDA仿真效率将不断提升,助力IC设计师设计出更复杂更高性能的IC产品。

未来,电子创新网芯英雄联盟未来还将就EDA仿真数据的可靠性存储、最佳实践、新兴技术应用等举办系列直播活动,敬请关注。欢迎关注芯英雄联盟微信号获取直播信息。

如您想回看《EDA仿真最新趋势和效率提升》直播,可以通过识别二维码观看

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利