Synopsys最近为其DDR5和DDR4以及使用5纳米制造技术的下一代系统级芯片控制器创建了一个新的物理接口。这将使制造SoC的厂商能够利用5纳米节点获得对DDR5和DDR4内存的额外支持。Synopsys目前是该接口的领导者,提供高达6400MT/s的数据传输率。

Synopsys使用内部的DesignWare IP,为芯片开发商提供服务,无论是SoC、SSD控制器还是CPU,都可以将物理接口和控制器IP安装到5纳米架构中,并确保所有系统使用Synopsys提供的经过验证的IP正确处理。

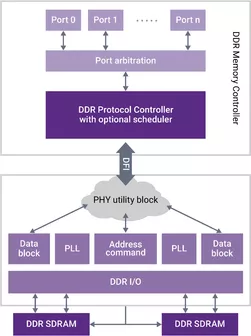

DesignWare IP结构包括一个用于DDR5和DDR4内存模块的控制器,具有命令调度器、双通道支持、ECC内存(可选)、内存协议处理器和DFI 5.0物理接口。它具有64个CAM条目,用于读取和写入内存模块,以及处理低至8个时钟周期的各种延迟水平。

Synopsys DesignWare IP是利用Arm AMBA 3.0 APB接口进行编程的。该公司还利用设计和重用程序提供经过硅验证的DDR5和DDR4物理层。该应用支持高达6400MT/s的数据传输率和内存的子系统,在它的结构中允许多达四个物理等级,其物理控制器及其物理控制器支持所有JEDEC标准的DDR5和DDR4运用。

稿源:cnBeta.COM