作者:电子创新网张国斌

当前,随着数智化的深入,人类社会正加速迈入智能世界,5G、人工智能、云计算等数字技术的融合发展和普及应用,正深刻改变人们的生活与生产方式,以联接和算力为代表的新一代数字基础设施,已经成为经济社会发展的关键基础和核心生产力,算力已经成为推动GDP发展的一种新要素,算力就是生产力!据悉,算力指数平均每提高一个点,就会带动国家数字经济和GDP分别增长3.5‰和1.8‰,因此,各国都在努力提升算力水平。

算力其实就是计算能力,作为硬件的基础指标,它一定是与具体硬件相关的,这就是高性能计算设备。在高性能计算设备中,除了我们熟悉的CPU、GPU、NPU和FPGA之外,还有其他关键器件和IP ,目前这个领域,本土公司正发起冲击,在近日召开的2023中国临港国际半导体大会上,芯动科技IP研发副总裁高专在专题发言中就分享了芯动科的高性能计算IP“三件套”:HBM/DDRn、Chiplet、SerDes。

他指出不管是在云端的大模型或者AI,或者是边缘端、终端,都需要涉及到接口、内存、带宽,而芯动科技就是一个专业做接口IP的公司,已经走过17年发展之路,芯动科技的接口IP主要集中在三件套:DDRn、SerDes、Chiplet。

“整个IP的市场规模不大,可能就60亿美元,但是它撬动的是整个芯片设计行业,包括半导体市场,还有整个电子消费市场,是一个巨大的杠杆,也就是IP是赋能,是为芯片设计行业提供弹药、基础砖瓦的领域。”他指出,“先进工艺下面如果要做一个芯片,你的IP非常关键,在一些竞争比较激烈的领域,大家用的工艺是一样的,封装、CPU等都是一样的,这时候需要IP来实现差异化。”

他表示芯动科技是一站式的IP和定制芯片供应商,芯动科技的IP覆盖的工艺非常全,不管是TSMC,还是中芯国际,还是三星、UMC、华立,这些厂的工艺节点都覆盖,并且芯动科技在最先进的7纳米、6纳米、5纳米、3纳米上都有IP布局。

“我们17年专注做IP,有两三百家客户使用我们的IP去量产。芯动科技可以提供整套接口IP的解决方案,包括高速IP,以及Video、Audio包括Mixed Signal IP,其中High Speed的IP是高性能SOC必不可少的。更先进的GDDR7、HBM4、LPDDR6、HBM4都在研发中。”他表示。

据他介绍,芯动科技的IP有三个特点:

第一,支持的协议非常先进,不管是GDDR6/6X,还是HBM3,还是DDR5、LPDDR5,都是现今中我们可以看到在一些高端芯片上正在用的,或者市面上能用到的最先进的接口IP。

第二,支持的工艺非常先进,3纳米已经流片数次;

第三、IP客户群上非常多,有非常多的量产经验。

如上图所示,TSMCIP合作伙伴全球37家,芯动科技是其中之一,而且芯动科技是大陆唯一的TSMC官方IP合作伙伴。

芯动科的高性能计算IP“三件套”

1、DDR系列。

目前主流的所有DDR系列接口IP,不管是服务器CPU使用的DDR5/4,还是在一些手机和高端的消费电子使用LPDDR5/4,以及在一些AI、GPU上使用的GDDR6/6X。还有HBM3/2E,芯动科技都可以提供。

“此外,我们所有的接口IP都是有量产或者测试的,例如我提到的GDDR新东西,标准没发布,我们正在做,没验证不拿出来讲,但这些拿出来说的确实有量产,我们在全球来说其实是对DDR接口技术覆盖最全的IP公司。”他强调,“举例来说,LPDDR5X跑到10G比特每秒,最高标准是8533,我们超频超到10G比特每秒,单端信号,我们的DDR5 5.6G的测试眼图可以看到。刚刚说GDDR6单根信号跑到18G比特每秒的眼图,GDDR6X跑到24G比特每秒,并且GDDR6X是单端信号PAM4的。多说一句,PAM4信号在56G和112G用得非常多,但是在单端信号上用PAM4其实是很少见的,在GDDR6X使用了这个,并且可以和GDDR6兼容,GDDR7回到PAM3的信号调制方式,我们正在研发。”

“还有HBM3和2E,这是大模型训练必不可少的,不管是英伟达,还是AMD,所有的高性能计算、大算力上的基本上都是HBM的东西,我们为HBM3专门做了测试片,并且我们的HBM是3和2E可以Combo设计。Combo的好处是可以同一颗芯片既支持3,也支持2E,也就是当HBM价格波动剧烈的时候,可以有更多选择。”他强调。

2、Chiplet。

目前Chiplet非常火爆,被看成是延续摩尔定律的不二选择,高专表示芯动科技在Chiplet有多年研发积累,芯动科技已经发布了Chiplet INNOLINK ABC方案,这个方案是单端信号做Chiplet互联。随着去年UCle的标准发布,芯动科技发现这个方案和他们的方案非常接近,用单端信号做Chiplet的互联,并且标准封装和先进封装用不同的方案。

INNOLINK分成ABC三类:

第一个,基于SerDes的互联,也就是程序的衰减比较大。

第二个,基于有机物基板互联,它的最大好处是可以兼容传统的Flip chip封装,不需要去做2.5D的东西。

第三个是专门针对于Silicon interposer做的优化,支持的是Micro bump,也就是Bump pitch55微米左右,或者更小的Bump pitch都可以支持,它的互联带宽和功耗要求更低,它需要用2.5D的方式去集成。

上图是芯动科技基于PCB和有机物基板封装时测试的单端信号18G比特每秒和20G比特每秒的测试眼图,INNOLINK-B。

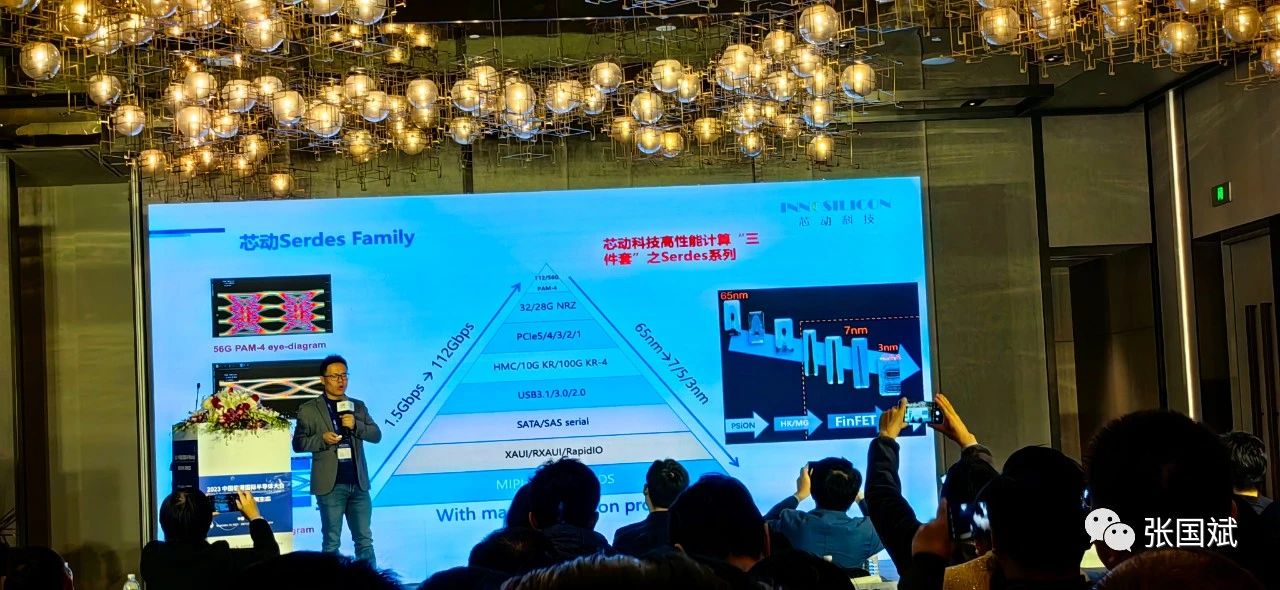

3、SerDes系列

据他介绍,一系列基于SerDes的接口协议包括SATA、PCle、USB都SerDes的产品范畴。“芯动科技的SerDes有一些特点,如我们的功耗比较低,成本比较好,在集成或者做定制化,比如很多客户需要Multi mode protected service,也就是它支持多种协议的SerDes,有时候可以当PCle用,有时候可以当USB3用,还可以当别的各种协议来用,这种时候你在集成的时候,可以有一些灵活性,有的不需要可以拿掉,具有一些灵活性。”他表示。

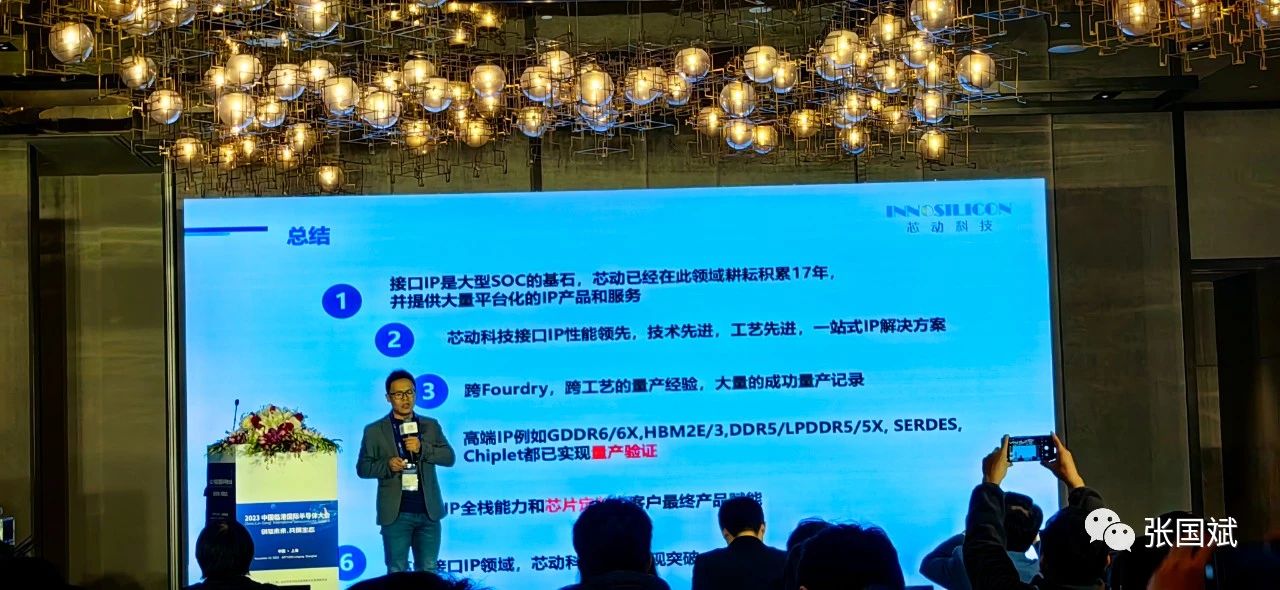

他总结说接口IP是大型SOC的基石,芯动科技在这个领域艰苦研发了17年,芯动科技的IP已经有很多客户在量产,同时芯动科技基于IP全栈的能力,也可以为客户提供一些芯片定制的服务,这是基于IP的相互耦合和赋能。所以高端接口IP方面,从国产的角度来说,芯动科技其实已经有相当大的突破!

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利