LEC2 Workbench系列技术博文主要关注莱迪思产品的应用开发问题。这些文章由莱迪思教育能力中心(LEC2)的FPGA设计专家撰写。LEC2是专门针对莱迪思屡获殊荣的低功耗FPGA和解决方案集合的全球官方培训服务供应商。

莱迪思CrossLink™-NX FPGA拥有丰富的特性,可加速实现高速和低速接口。本文(系列博文的第一篇)描述了使用CrossLink-NX FPGA连接基于SPI的外部组件。第一篇博文介绍了使用两个时钟域实现连接DAC(亚德诺半导体公司的AD7303 DAC)的SPI接口。第二篇博文将介绍使用单个时钟域实现连接ADC(亚德诺半导体公司的 ADC AD7476)的SPI接口。两个案例中呈现了两种截然不同的实现接口的方法。

两个时钟域的实现方案(dac_2c)

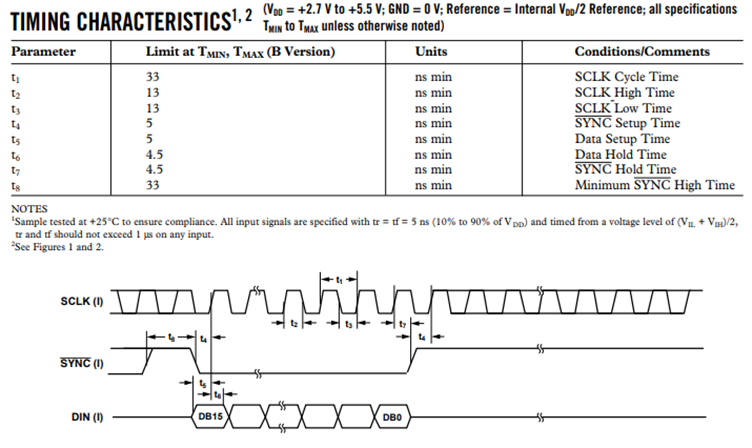

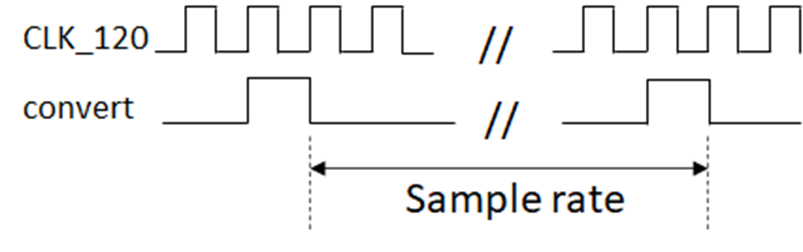

亚德诺半导体公司(ADI)的AD7303模块用作外部DAC。图1显示了接口的时序图和时序参数。在本例中,SCLK频率为30 MHz。时序参数t4、t5和t6在时序约束规范时尤其需要关注,它们将在set_output_delay约束中使用。

图1:时序图和时序特征

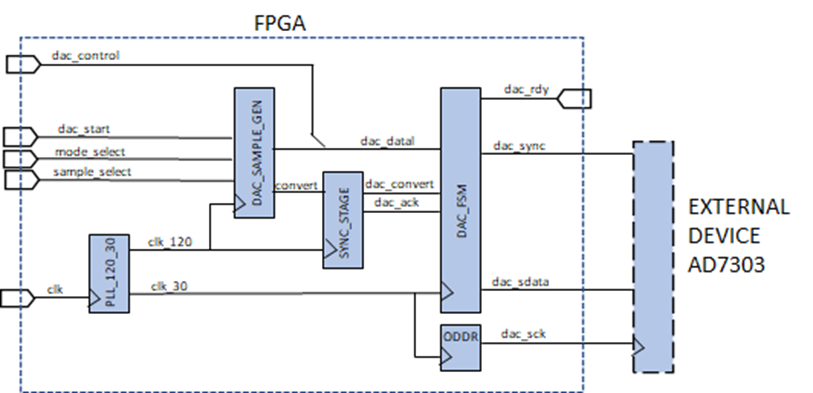

两个时钟域解决方案的实现如图2所示。

图2:两个时钟域SPI接口的实现

使用的参数:

输入时钟频率:100 MHZ

内部时钟CLK_120频率:120 MHZ

内部时钟CLK_30频率:30 MHZ

生成的时钟dac_sck:30 MHZ

PLL_120_30

PLL从外部时钟CLK(100 MHz)生成两个内部相位同步时钟CLK_120和CLK_30。

dac_sample_gen模块

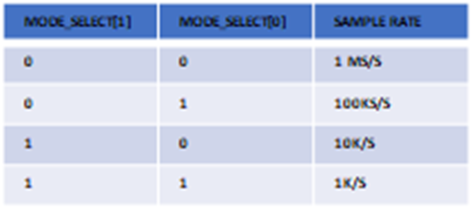

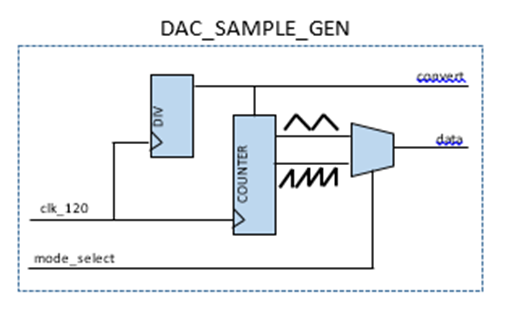

dac_sample_gen模块为dac_fsm生成采样信号(转换)。采样信号开始向DAC传输数字数据。采样率通过sample_select [1:0]信号设置,如表1所示。dac_sample_gen的框图如图3所示。

表1:采样率设置

图3:dac_sample_gen的框图

mode_select控制信号控制方波信号或三角波信号的生成,作为DAC的输入数据。

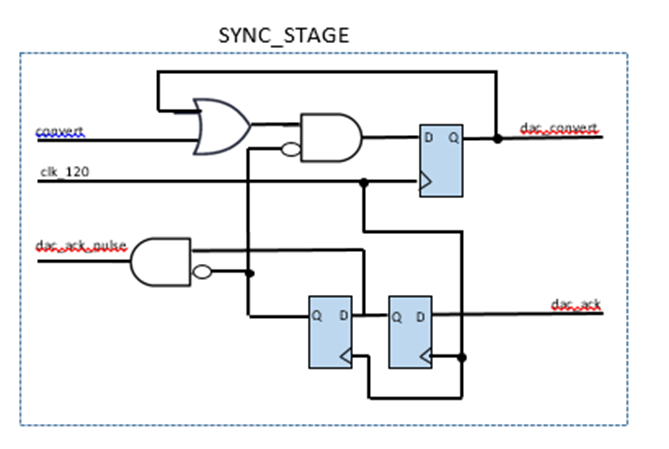

sync_stage模块

dac_sample_gen模块与CLK_120一起工作。控制单元dac_fsm是CLK_30域的一部分。sync_stage模块将转换信号从CLK_120域传输到CLK_30域。来自dac_fsm的相应信号从CLK_30域传输到CLK_120。sync_stage的框图如图4所示。

图4:sync_stage的框图

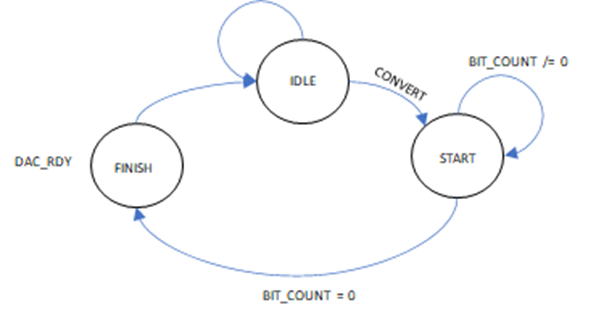

dac_fsm模块用于双时钟实现方案

dac_fsm模块控制生成传输到DAC的控制/数据信号。为了遵循图1给出的t4、t5和t6的值,dac_fsm在CLK_30的下降沿工作。Dac_fsm作为状态机实现。

图5:控制结构dac_fsm状态机转换信号被识别后,bit_count计数器加载值15。串行数据在时钟信号CLK_30的下降沿输出到dac_sdata上。传输16位数据后,dac_fsm再次发出就绪信号并等待下一个转换信号。

约束两个时钟域解决方案的设计

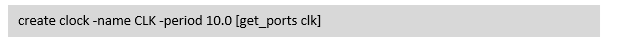

1. 约束时钟CLK

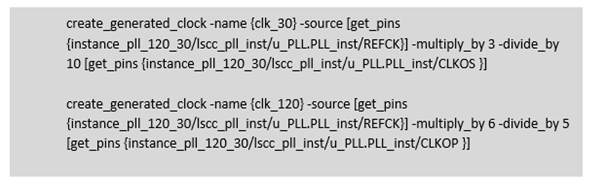

2. 约束时钟CLK_120和CLK_30

无需明确定义CLK_120和CLK_30这两个时钟信号,因为它们会由设计软件自动定义。这两个时钟也称为自动生成时钟。

3. 约束dac_clk

连接到端口dac_sck的时钟信号是内部时钟CLK_30的副本。该信号被外部DAC解读为时钟。因此,该信号也必须被定义为时钟,便于正确描述t4、t5和t6的时间要求。该时钟即所谓的手动生成时钟。

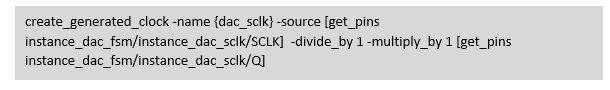

4. 约束DAS输入/FPGA输出

时间值t4、t5和t6描述了外部模块的setup/hold要求。这些要求使用 set_output_delay约束进行描述。

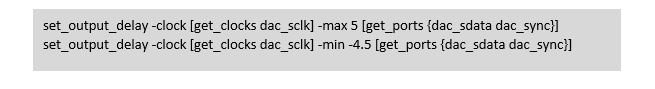

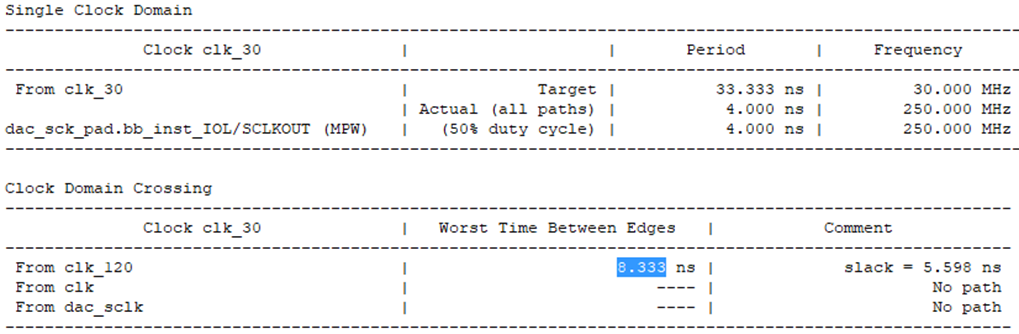

运行两个时钟域解决方案的时序分析

时序分析报告显示了两个时钟信号CLK_120和CLK_30之间的关系。

注意CLK_120和CLK_30的跨时钟域参数,反之亦然。这正是我们所期望的。

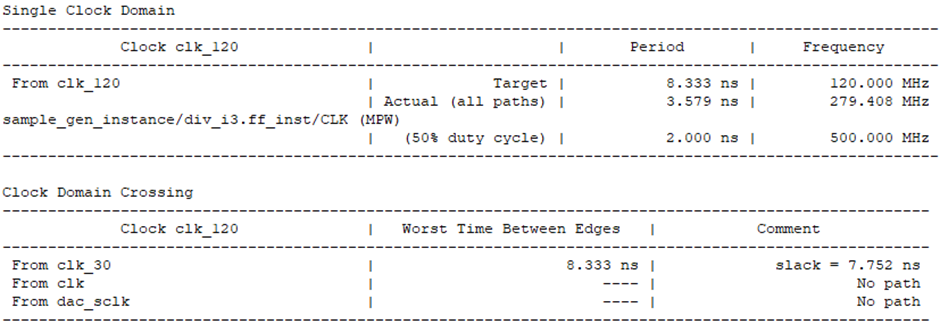

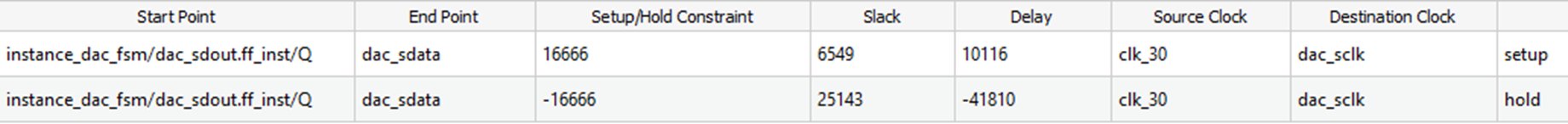

对输出信号dac_sync和dac_sdata的分析展示了基于set_output_delay约束实现的setup slack和hold slack。

总结总之,两个时钟域提供了一些功耗方面的优势,因为设计的一部分以较低的速度运行。此外,时序约束也很容易指定。该项目(dac_2c)可在LEC2索取。欲获取项目副本,请通过info@lec2-fpga.com与我们联系。

我们将在下一篇文章中探讨单个时钟域的方法。

Eugen Krassin是莱迪思教育能力中心(LEC2)的总裁兼创始人。